Pin description – Rainbow Electronics MAX5890 User Manual

Page 8

MAX5890

14-Bit, 600Msps, High-Dynamic-Performance

DAC with LVDS Inputs

8

_______________________________________________________________________________________

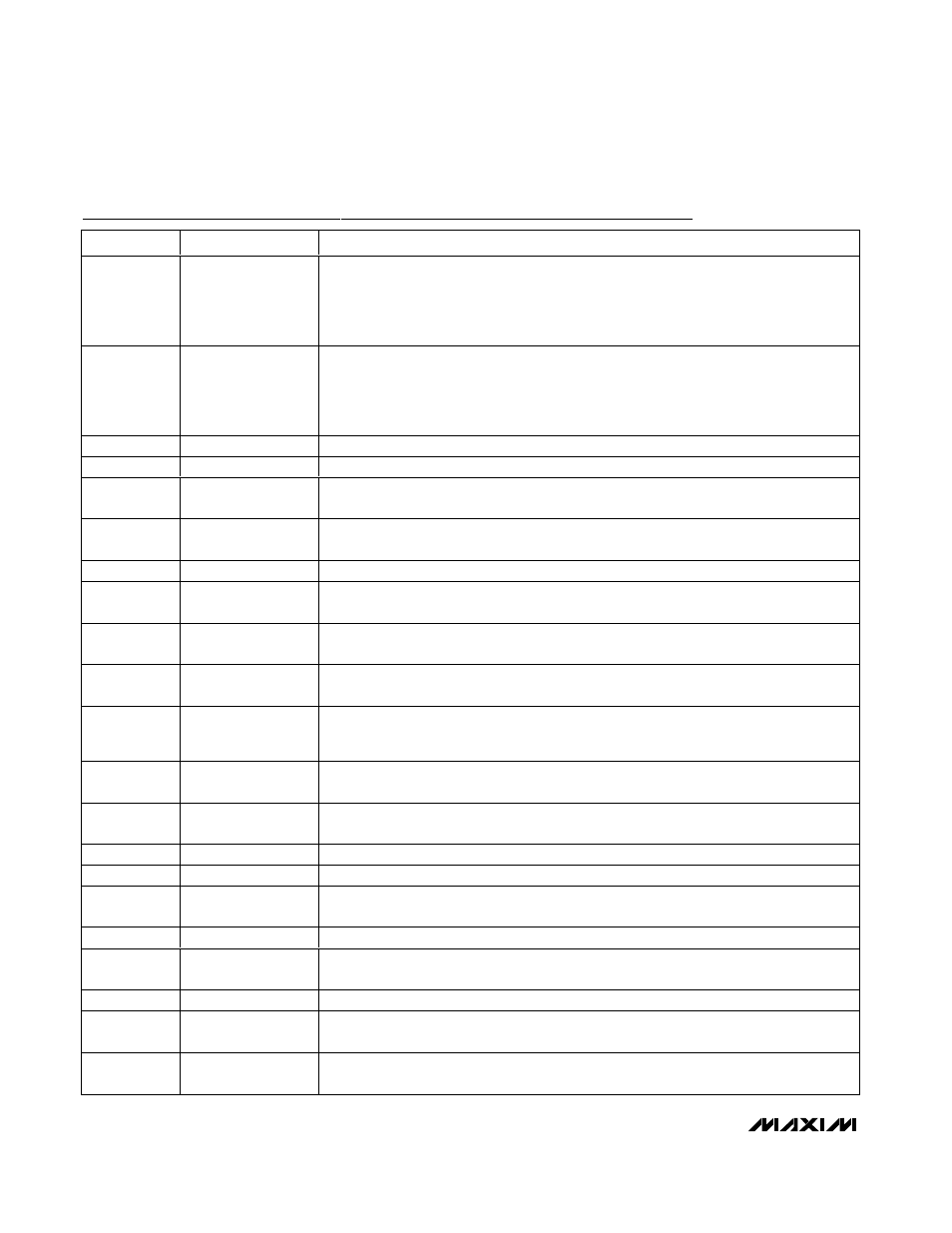

PIN

NAME

FUNCTION

1, 3, 5, 46, 48,

50, 52, 54, 56,

58, 60, 63, 65,

67

D2N, D1N, D0N,

D13N, D12N, D11N,

D10N, D9N, D8N,

D7N, D6N, D5N,

D4N, D3N

Differential Negative LVDS Inputs. Data bits D0–D13 (offset binary format).

2, 4, 45, 47,

49, 51, 53, 55,

57, 59, 62, 64,

66, 68

D1P, D0P, D13P,

D12P, D11P, D10P,

D9P, D8P, D7P, D6P,

D5P, D4P, D3P, D2P

Differential Positive LVDS Inputs. Data bits D0–D13 (offset binary format).

6–9

N.C.

No Connection. Leave floating or connect to DGND.

10

DGND

Digital Ground. Ground return for DV

DD3.3

and DV

DD1.8

.

11

DV

DD3.3

Digital Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass with a

0.1µF capacitor to DGND.

12

PD

Power-Down Input. Set PD high to force the DAC into power-down mode. Set PD low for

normal operation. PD has an internal 2µA pulldown.

13, 42, 43, 44

N.C.

No Connection. Leave floating or connect to AGND.

14, 21, 22, 25,

26, 31, 32

AV

DD3.3

Analog Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass with a

0.1µF capacitor to AGND.

15, 20, 23, 24,

27, 30, 33

AGND

Analog Ground. Ground return for AV

DD3.3

and AV

DD1.8

.

16

REFIO

Reference I/O. Output of the internal 1.2V precision bandgap reference. Bypass with a

0.1µF capacitor to AGND. REFIO can be driven with an external reference source.

17

FSADJ

Full-Scale Current Adjustment. Connect an external resistor R

SET

between FSADJ and

DACREF to set the output full-scale current. The output full-scale current is equal to 32 x

V

REF

/ R

SET

.

18

DACREF

Current-Set Resistor Return Path. Internally connected to ground, but do not use as

ground connection.

19, 34, 35

AV

DD1.8

Analog Supply Voltage. Accepts a 1.71V to 1.89V supply voltage range. Bypass with a

0.1µF capacitor to AGND.

28

OUTN

Complementary DAC Output. Negative terminal for current output.

29

OUTP

DAC Output. Positive terminal for current output.

36, 41

AV

CLK

Clock Supply Voltage. Accepts a 3.135V to 3.465V supply voltage range. Bypass with a

0.1µF capacitor to CGND.

37, 40

CGND

Clock Supply Ground

38

CLKN

Complementary Converter Clock Input. Negative input terminal for differential converter

clock.

39

CLKP

Converter Clock Input. Positive input terminal for differential converter clock.

61

DV

DD1.8

Digital Supply Voltage. Accepts a 1.71V to 1.89V supply voltage range. Bypass with a

0.1µF capacitor to DGND.

—

EP

Exposed Pad. Must be connected to common point for AGND, DGND, and CGND through

a low-impedance path. EP is internally connected to AGND, DGND, and CGND.

Pin Description