Internal linear regulator (reg), Internal uvlo/external uvlo – Rainbow Electronics MAX5081 User Manual

Page 9

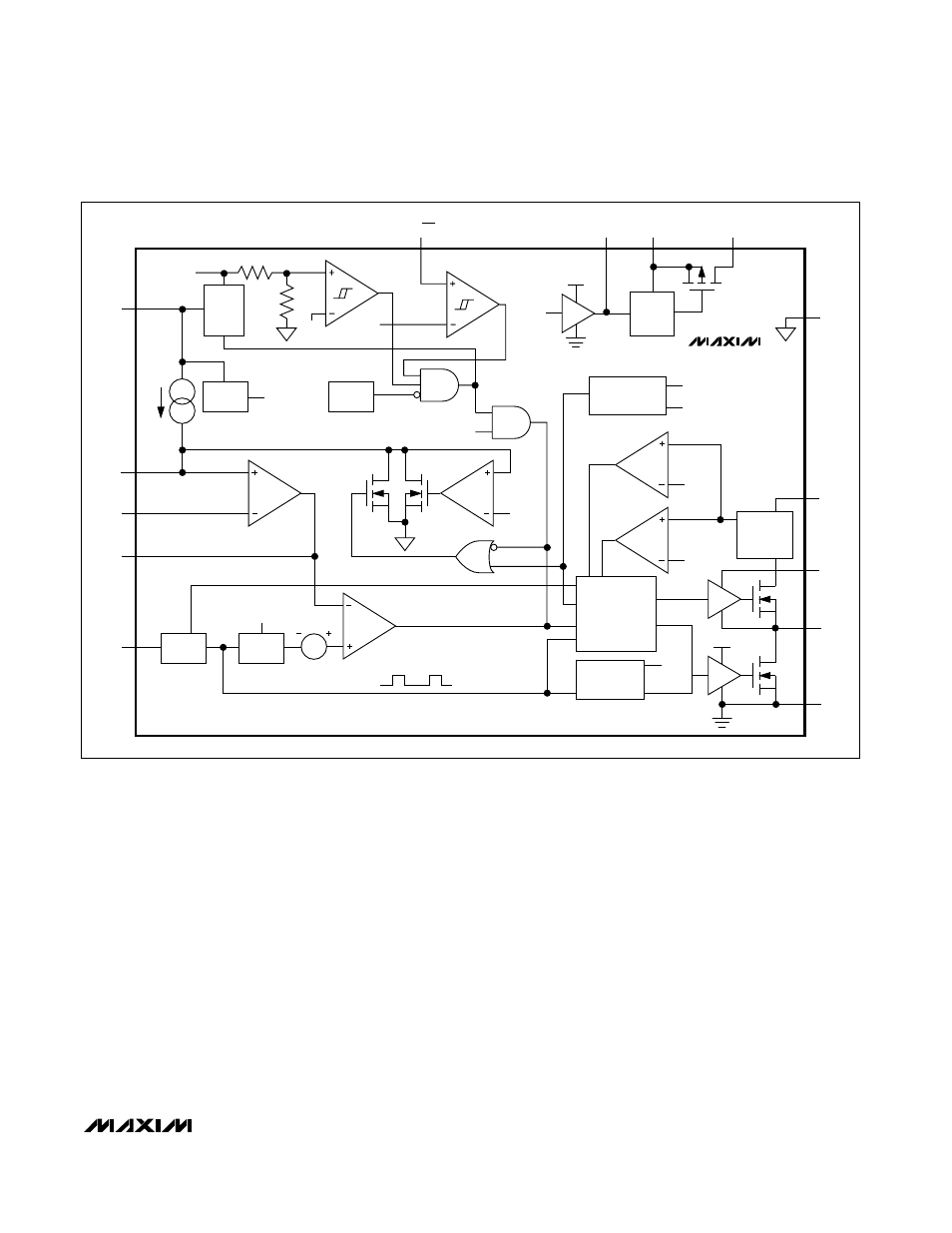

MAX5080/MAX5081

1A, 40V, MAXPower Step-Down

DC-DC Converters

_______________________________________________________________________________________

9

Internal Linear Regulator (REG)

REG is the output terminal of a 5V (MAX5080), or 8V

(MAX5081) LDO which is powered from IN and pro-

vides power to the IC. Connect REG externally to

DVREG to provide power for the high-side MOSFET

gate driver. Bypass REG to SGND with a ceramic

capacitor of at least 1µF. Place the capacitor physically

close to the MAX5080/MAX5081 to provide good

bypassing. During normal operation, REG is intended

for powering up only the internal circuitry and should

not be used to supply power to external loads.

Internal UVLO/External UVLO

The MAX5080/MAX5081 provides two undervoltage

lockouts (UVLOs). An internal UVLO looks at the input

voltage (V

IN

) and is fixed at 4.1V (MAX5080) or 7.1V

(MAX5081). An external UVLO is sensed and pro-

grammed at the ON/OFF pin. The external UVLO over-

rides the internal UVLO when the external UVLO is

higher than the internal UVLO. During startup, before

any operation begins, the input voltage and the voltage

at ON/OFF must exceed their respective UVLOs. The

external UVLO has a rising threshold of 1.23V with

0.12V of hysteresis. Program the external UVLO by

connecting a resistive divider from IN to ON/OFF to

SGND. Connect ON/OFF to IN directly to disable the

external UVLO.

Driving ON/OFF to ground places the MAX5080/

MAX5081 in shutdown. When in shutdown the internal

power MOSFET turns off, all internal circuitry shuts

down and the quiescent supply current reduces to

200µA. Connect an RC network from ON/OFF to SGND

to set a turn-on delay that can be used to sequence the

output voltages of multiple devices.

MAX5080

1.23V

1.23V

ON/OFF

DVREG

PCLK

LDO

EN

IN

REG

SS

FB

THERMAL

SHDN

REF

IN

0.3V

CLK

1.23V

REGOK

EN

V

REF

V

REF

I

SS

>1.23V ON

<1.11V OFF

COMP

SYNC

E/A

SSA

CPWM

RAMP

LOGIC

EN

OSC

CHARGE-PUMP

MANAGEMENT

PCLK

BST

IN

SGND

LX

PGND

SCLK

HIGH-SIDE

CURRENT

SENSE

REF_PFM

PFM

REF_ILIM

ILIM

OVERL

CLK

ILIM

OVERLOAD

MANAGEMENT

DVREG

C+

DVREG

C-

LEVEL

SHIFT

Figure 1. MAX5080 Simplified Block Diagram