Applications information – Rainbow Electronics ADC14061 User Manual

Page 18

Applications Information

(Continued)

6.0 DYNAMIC PERFORMANCE

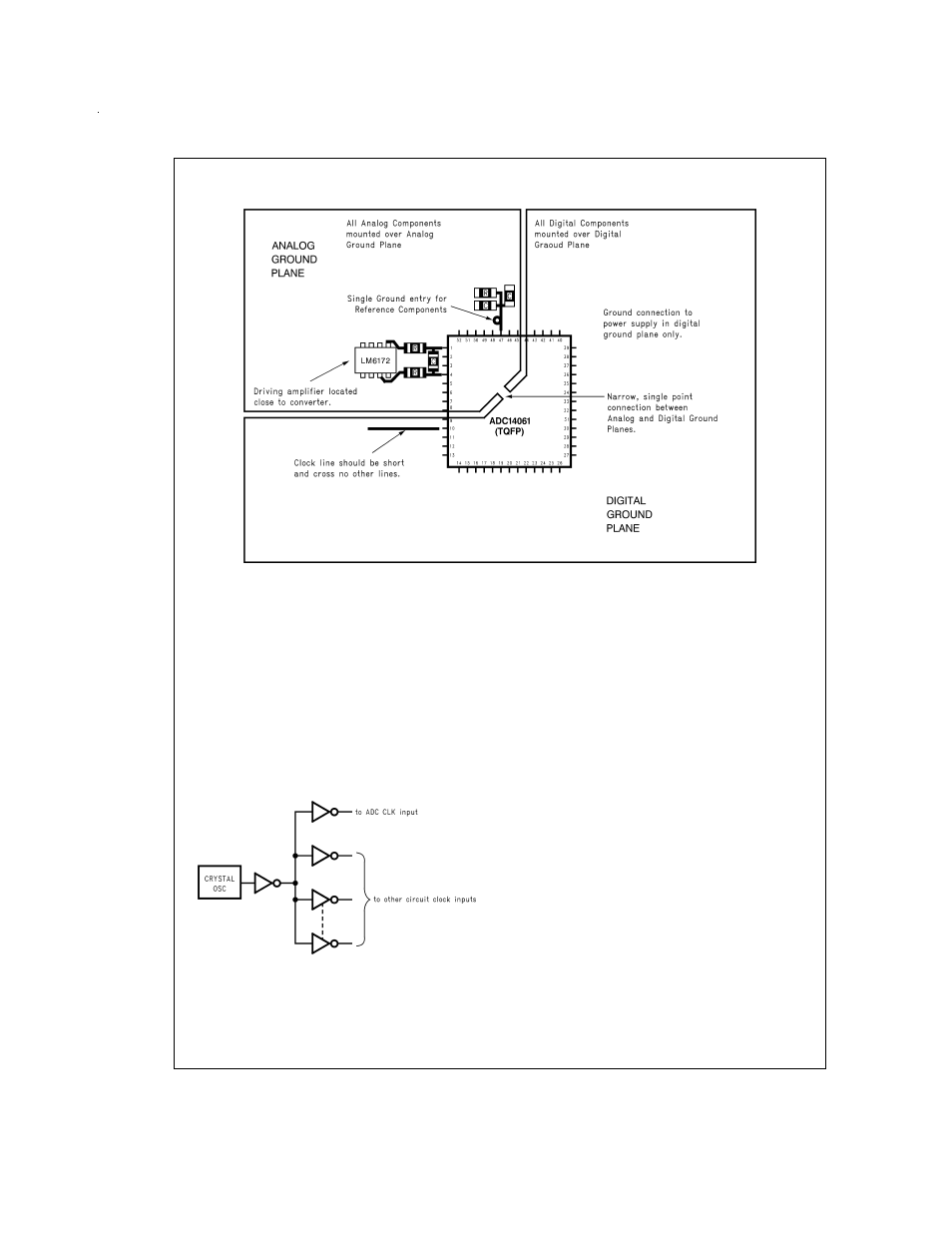

The ADC14061 can achieve impressive dynamic perfor-

mance. To achieve the best dynamic performance with the

ADC14061, the clock source driving the CLK input must be

free of jitter. For best ac performance, isolate the ADC clock

from any digital circuitry with buffers, as with the clock tree

shown in

Figure 10

.

As mentioned in section 5.0, it is good practice to keep the

ADC clock line as short as possible and to keep it well away

from any other signals. Other signals can introduce phase

noise (jitter) into the clock signal, which can lead to in-

creased distortion. Even lines with 90˚ crossings have ca-

pacitive coupling, so try to avoid even these 90˚ crossings of

the clock line.

7.0 COMMON APPLICATION PITFALLS

Driving the inputs (analog or digital) beyond the power

supply rails. For proper operation, all inputs should not go

more than 100 mV beyond the supply rails (more than 100

mV below the ground pins or 100 mV above the supply pins).

Exceeding these limits on even a transient basis may cause

faulty or erratic operation. It is not uncommon for high speed

digital circuits (e.g., 74F and 74AC devices) to exhibit under-

shoot that goes more than a volt below ground. A resistor of

about 50 to 100

Ω

in series with the offending digital input will

eliminate the problem.

Do not allow input voltages to exceed the supply voltage dur-

ing power up.

Be careful not to overdrive the inputs of the ADC14061 with

a device that is powered from supplies outside the range of

the ADC14061 supply. Such practice may lead to conversion

inaccuracies and even to device damage.

Attempting to drive a high capacitance digital data bus.

The more capacitance the output drivers must charge for

each conversion, the more instantaneous digital current

flows through V

D

I/O and DGND I/O. These large charging

current spikes can couple into the analog circuitry of the

ADC14061, degrading dynamic performance. Adequate by-

passing and maintaining separate analog and digital ground

planes will reduce this problem. The digital data outputs

should be buffered (with 74ACQ541, for example). Dynamic

performance can also be improved by adding series resis-

tors at each digital output, close to the ADC14061, which re-

duces the energy coupled back into the converter output

pins by limiting the output current. A reasonable value for

these resistors is 47

Ω

.

Using an inadequate amplifier to drive the analog input.

As explained in Section 1.3, the capacitance seen at the in-

DS100103-23

FIGURE 9. Example at a suitable layout.

DS100103-24

FIGURE 10. Isolating the ADC clock from other

circuitry with a clock tree.

www.national.com

18