Applications information – Rainbow Electronics ADC14061 User Manual

Page 14

Applications Information

(Continued)

The sign bit of the output word will be a logic low when V

IN

+

is greater than V

IN

− . When V

IN

+ is less than V

IN

−, the sign

bit of the output word will be a logic high.

For single ended operation, one of the analog inputs should

be connected to V

CM

. However, SNR and SINAD are re-

duced by about 12dB with a single ended input as compared

with differential inputs.

An input voltage of V

IN

= (V

IN

+) − (V

IN

−) = 0 will be inter-

preted as mid-scale and will thus be converted to

00,0000,0000,0000, plus any offset error.

The V

IN

+ and the V

IN

− inputs of the ADC14061 consist of an

analog switch followed by a switched-capacitor amplifier.

The capacitance seen at the analog input pins changes with

the clock level, appearing as 12 pF when the clock is low,

and 28 pF when the clock is high. It is recommended that the

ADC14061 be driven with a low impedance source of 100

Ohms or less.

A simple application circuit is shown in

Figure 6

and

Figure 7

.

Here we use two LM6172 dual amplifiers to provide a bal-

anced input to the ADC14061. Note that better noise perfor-

mance is achieved when V

REF

+

IN

voltage is forced with a

well-bypassed resistive divider. The resulting offset and off-

set drift is minimal.

Since a dynamic capacitance is more difficult to drive than is

a fixed capacitance, choose driving amplifiers carefully. The

CLC427, CLC440, LM6152, LM6154, LM6172, LM6181 and

LM6182 are excellent amplifiers for driving the ADC14061.

1.4 V

CM

Analog Inputs

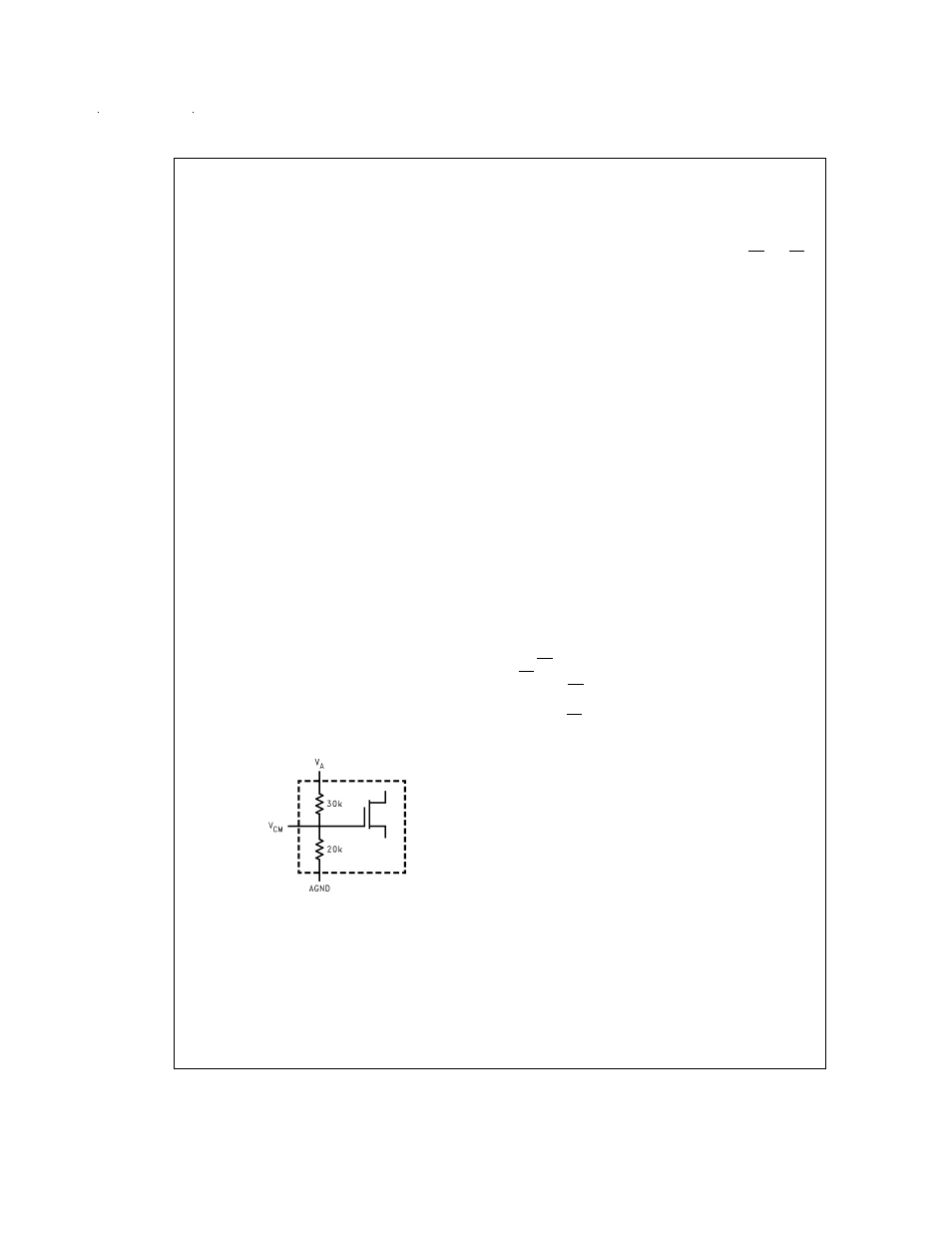

The V

CM

input of the ADC14061 is internally biased to 40%

of the V

A

supply with on-chip resistors, as shown in

Figure 5

.

The V

CM

pin must be bypassed to prevent any power supply

noise from modulating this voltage. Modulation of the V

CM

potential will result in the introduction of noise into the input

signal. The advantage of simply bypassing V

CM

(without

driving it) is the circuit simplicity. On the other hand, if the V

A

supply can vary for any reason, V

CM

will also vary at a rate

and amplitude related to the RC filter created by the bypass

capacitor and the internal divider resistors. However, perfor-

mance of this approach will be adequate for many

applications.

By forcing V

CM

to a fixed potential, you can avoid the prob-

lems mentioned above. One such approach is to buffer the

2.0 Volt reference voltage to drive the V

CM

input, holding it at

a constant potential as shown in

Figure 6

and

Figure 8

. If the

reference voltage is different from the desired V

CM

, that de-

sired V

CM

voltage may be derived from the reference or from

another stable source.

Note that the buffer used for this purpose should be a slow,

low noise amplifier. The LMC660, LMC662, LMC272 and

LMC7101 are good choices for driving the V

CM

pin of the

ADC14061.

2.0 DIGITAL INPUTS

Digital Inputs consist of CLOCK, RESET, CAL, RD and PD.

2.1 The CLOCK signal drives an internal phase delay loop to

create timing for the ADC. Drive the clock input with a stable,

low phase jitter clock signal in the range of 300 kHz to 2.5

MHz. The trace carrying the clock signal should be as short

as possible. This trace should not cross any other signal line,

analog or digital, not even at 90˚.

The CLOCK signal also drives the internal state machine. If

the clock is interrupted, the data within the pipeline could be-

come corrupted.

A 100 Ohm damping resistor should be placed in series with

the CLOCK pin to prevent signal undershoot at that input.

2.2 The RESET input is level sensitive and must be pulsed

high for at least two clock cycles to reset the ADC after

power-up and before calibration (See Timing Diagram 2).

2.3 The CAL input is level sensitive and must be pulsed high

for at least two clock cycles to begin ADC calibration (See

Timing Diagram 2). Reset the ADC14061 before calibrating.

Re-calibrate after the temperature has changed by more

than 50˚C since the last calibration was performed and after

return from power down.

During calibration, use the same clock frequency that will be

used for conversions to avoid excessive offset errors.

Calibration takes 272,800 clock cycles. Irrelevant data may

appear at the data outputs during RESET or CAL and for 13

clock cycles thereafter. Calibration should not be started until

the reference outputs have settled (100mS with 1µF capaci-

tors on these outputs) after power up or coming out of the

power down mode.

2.4 RD pin is used to READ the conversion data. When the

RD pin is low, the output buffers go into the active state.

When the RD input is high, the output buffers are in the high

impedance state.

2.5 The PD pin, when low, holds the ADC14061 in a

power-down mode where power consumption is typically

less than 2mW to conserve power when the converter is not

being used. The ADC14061 will begin normal operation

within t

WU

after this pin is brought high, provided a valid

CLOCK input is present. Power dissipation during shut-down

is not affected by the clock frequency, or by whether there is

a clock signal present. The data in the pipeline is corrupted

while in the power down mode. The ADC14061 should be re-

set and calibrated upon returning to normal operation after a

power down.

3.0 OUTPUTS

The ADC14061 has four analog outputs: V

REF

+

OUT

,

V

REF

−

OUT

, V

REF (MID)

and V

CM

.There are 15 digital outputs:

EOC (End of Conversion) and 14 Data Output pins.

3.1 The reference output voltages are made available only

for the purpose of bypassing with capacitors. These pins

should not be loaded with more than 10 µA DC. These output

voltages are described as

V

REF

+

OUT

= V

CM

+

1

⁄

2

V

REF

V

REF

−

OUT

= V

CM

−

1

⁄

2

V

REF

where V

REF

= (V

REF

+

IN

) − (V

REF

+ IN)

V

REF (MID)

= (V

REF

+

OUT

+ V

REF

−

OUT

) / 2.

DS100103-21

FIGURE 5. V

CM

input to the ADC14061 V

CM

is set to

40% of V

A

with on-chip resistors. Performance is

improved when V

CM

is driven with a stable, low

impedance source

www.national.com

14