Application hints – Rainbow Electronics ADC12138 User Manual

Page 33

Application Hints

(Continued)

6 0 INPUT SOURCE RESISTANCE

For low impedance voltage sources (

k

600X) the input

charging current will decay before the end of the S H’s

acquisition time of 2 ms (10 CCLK periods with f

CK

e

5 MHz) to a value that will not introduce any conversion

errors For high source impedances the S H’s acquisition

time can be increased to 18 or 34 CCLK periods For less

ADC accuracy and or slower CCLK frequencies the S H’s

acquisition time may be decreased to 6 CCLK periods To

determine the number of clock periods (N

c

) required for the

acquisition time with a specific source impedance for the

various resolutions the following equations can be used

12 Bit a Sign

N

C

e

R

S

a

2 3

c

f

CK

c

0 824

Where f

CK

is the conversion clock (CCLK) frequency in MHz

and R

S

is the external source resistance in kX As an exam-

ple operating with a resolution of 12 Bitsasign a 5 MHz

clock frequency and maximum acquistion time of 34 conver-

sion clock periods the ADC’s analog inputs can handle a

source impedance as high as 6 kX The acquisition time

may also be extended to compensate for the settling or

response time of external circuitry connected between the

MUXOUT and A DIN pins

The acquisition time t

A

is started by a falling edge of SCLK

and ended by a rising edge of CCLK (see timing diagrams)

If SCLK and CCLK are asynchronous one extra CCLK clock

period may be inserted into the programmed acquisition

time for synchronization

Therefore with asnychronous

SCLK and CCLKs the acquisition time will change from con-

version to conversion

7 0 INPUT BYPASS CAPACITANCE

External capacitors (0 01 mF – 0 1 mF) can be connected be-

tween the analog input pins CH0 – CH7 and analog ground

to filter any noise caused by inductive pickup associated

with long input leads These capacitors will not degrade the

conversion accuracy

8 0 NOISE

The leads to each of the analog multiplexer input pins

should be kept as short as possible This will minimize input

noise and clock frequency coupling that can cause conver-

sion errors Input filtering can be used to reduce the effects

of the noise sources

9 0 POWER SUPPLIES

Noise spikes on the V

A

a

and V

D

a

supply lines can cause

conversion errors the comparator will respond to the noise

The ADC is especially sensitive to any power supply spikes

that occur during the auto-zero or linearity correction The

minimum power supply bypassing capacitors recommended

are low inductance tantalum capacitors of 10 mF or greater

paralleled with 0 1 mF monolithic ceramic capacitors More

or different bypassing may be necessary depending on the

overall system requirements Separate bypass capacitors

should be used for the V

A

a

and V

D

a

supplies and placed

as close as possible to these pins

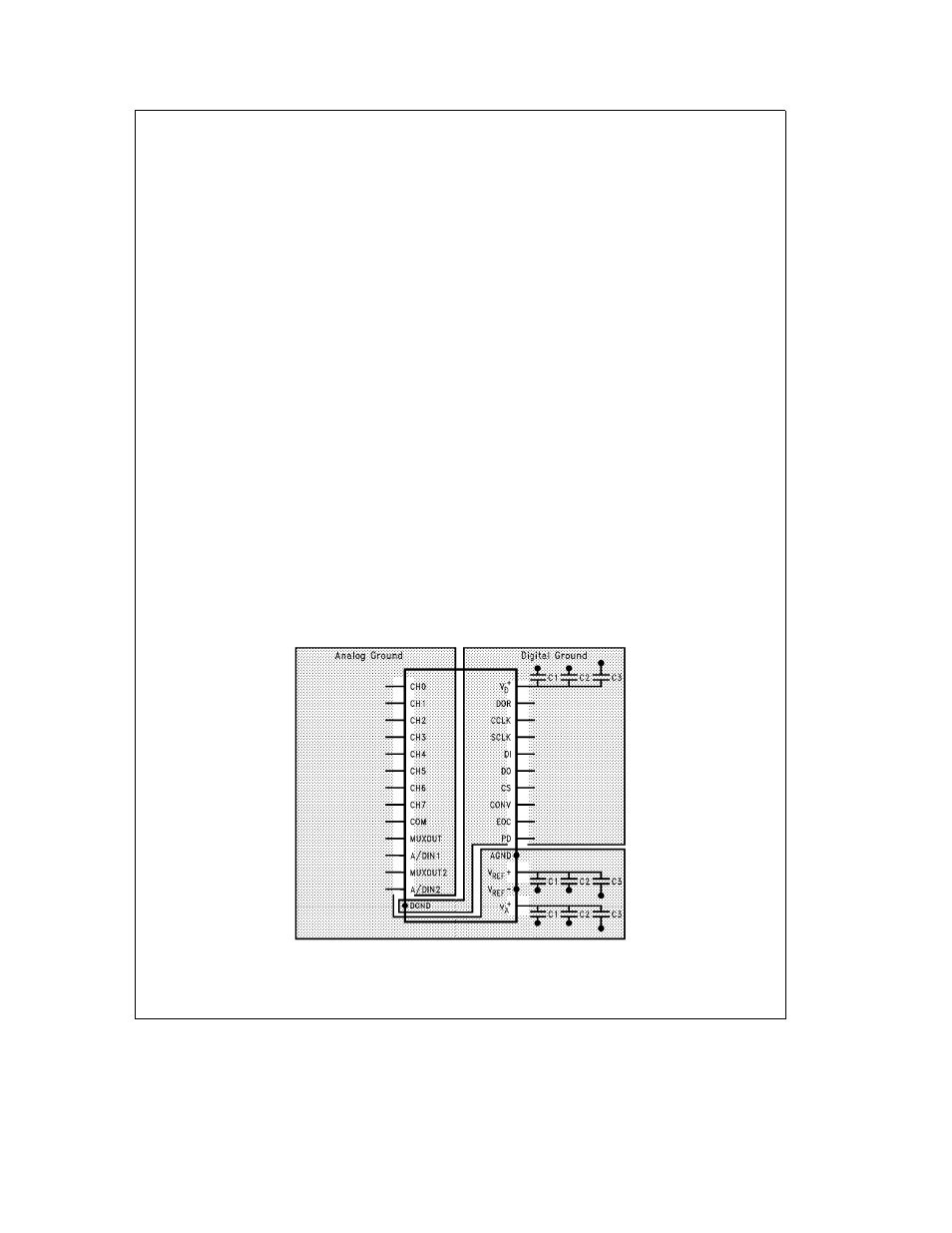

10 0 GROUNDING

The ADC12130 2 8’s performance can be maximized

through proper grounding techniques These include the

use of separate analog and digital ground planes The digi-

tal ground plane is placed under all components that handle

digital signals while the analog ground plane is placed un-

der all components that handle analog signals The digital

and analog ground planes are connected together at only

one point either the power supply ground or at the pins of

the ADC This greatly reduces the occurence of ground

loops and noise

Shown in

Figure 16

is the ideal ground plane layout for the

ADC12138 along with ideal placement of the bypass capaci-

tors The circuit board layout shown in

Figure 16

uses three

bypass capacitors 0 01 mF (C1) and 0 1 mF (C2) surface

mount capacitors and 10 mF (C3) tantalum capacitor

TL H 12079 – 45

FIGURE 16 Ideal Ground Plane

33