C slave addresses – Rainbow Electronics MAX5812 User Manual

Page 9

MAX5812

12-Bit Low-Power, 2-Wire, Serial

Voltage-Output DAC

_______________________________________________________________________________________

9

low transition on SDA with SCL high. A STOP condition

is a low-to-high transition on SDA while SCL is high

(Figure 2). A START condition from the master signals

the beginning of a transmission to the MAX5812. The

master terminates transmission by issuing a not

acknowledge followed by a STOP condition (see the

Acknowledge Bit section). The STOP condition frees the

bus. If a repeated START condition (S

r

) is generated

instead of a STOP condition, the bus remains active.

When a STOP condition or incorrect address is detect-

ed, the MAX5812 internally disconnects SCL from the

serial interface until the next START condition, minimiz-

ing digital noise and feedthrough.

Early STOP Conditions

The MAX5812 recognizes a STOP condition at any point

during transmission except when a STOP condition

occurs in the same high pulse as a START condition

(Figure 3). This condition is not a legal I

2

C format, at

least one clock pulse must separate any START and

STOP conditions.

Repeated START Conditions

A repeated start (S

r

) condition might indicate a change

of data direction on the bus. Such a change occurs

when a command word is required to initiate a read

operation. S

r

also can be used when the bus master is

writing to several I

2

C devices and does not want to

relinquish control of the bus. The MAX5812 serial inter-

face supports continuous write operations with or with-

out an S

r

condition separating them. Continuous read

operations require S

r

conditions because of the change

in direction of data flow.

Acknowledge Bit (ACK)

The acknowledge bit (ACK) is the ninth bit attached to

any 8-bit data word. ACK is always generated by the

receiving device. The MAX5812 generates an ACK

when receiving an address or data by pulling SDA low

during the ninth clock period. When transmitting data,

the MAX5812 waits for the receiving device to generate

an ACK. Monitoring ACK allows detection of unsuc-

cessful data transfers. An unsuccessful data transfer

occurs if a receiving device is busy or if a system fault

has occurred. In the event of an unsuccessful data

transfer, the bus master should reattempt communica-

tion at a later time.

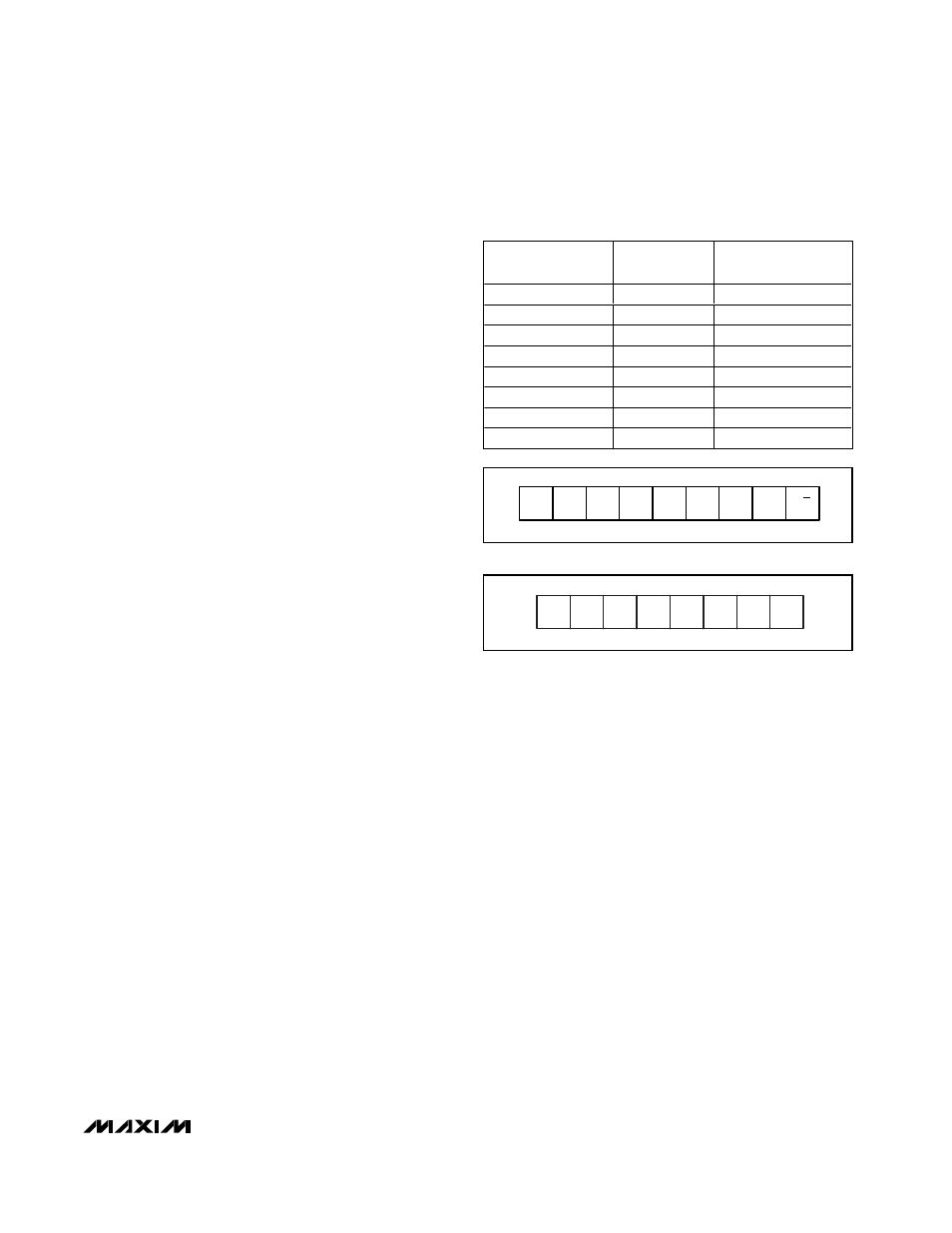

Slave Address

A bus master initiates communication with a slave

device by issuing a START condition followed by the

7-bit slave address (Figure 4). When idle, the MAX5812

waits for a START condition followed by its slave

address. The serial interface compares each address

value bit-by-bit, allowing the interface to power-down

immediately when an incorrect address is detected.

The LSB of the address word is the Read/Write (R/W)

bit. R/W indicates whether the master is writing to or

reading from the MAX5812 (R/W = 0 selects the write

condition, R/W = 1 selects the read condition). After

receiving the proper address, the MAX5812 issues an

ACK by pulling SDA low for one clock cycle.

The MAX5812 has eight factory/user-programmed

addresses (Table 2). Address bits A6 through A1 are

preset; A0 is controlled by ADD. Connecting ADD to

GND sets A0 = 0. Connecting ADD to V

DD

sets A0 = 1.

This feature allows up to eight MAX5812s to share a bus.

Write Data Format

In write mode (R/W = 0), data that follows the address

byte controls the MAX5812 (Figure 5). Bits C3–C0 con-

figure the MAX5812 (Table 3). Bits D11–D0 are DAC

data. Input and DAC registers update on the falling

edge of SCL during the acknowledge bit. Should the

write cycle be prematurely aborted, data will not be

updated and the write cycle must be repeated. Figure

6 shows two example write data sequences.

S

A6

A5

A4

A3

A2

A1

A0

R/W

Figure 4. Slave Address Byte Definition

Table 2. MAX5812 I

2

C Slave Addresses

PART

V

ADD

DEVICE ADDRESS

(A

6

...A

0

)

MAX5812L

GND

0010 000

MAX5812L

V

DD

0010 001

MAX5812M

GND

0010 010

MAX5812M

V

DD

0010 011

MAX5812N

GND

0110 100

MAX5812N

V

DD

0110 101

MAX5812P

GND

1010 100

MAX5812P

V

DD

1010 101

C3

C2

C1

C0

D11

D10

D9

D8

Figure 5. Command Byte Definition