Electrical characteristics – Rainbow Electronics ADC10738 User Manual

Page 8

Electrical Characteristics

(Continued)

Note 1

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur

Note 2

Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits For guaranteed specifcations and

test conditions see the Electrical Characteristics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may

degrade when the device is not operated under the listed test conditions

Note 3

All voltages are measured with respect to GND unless otherwise specified

Note 4

When the input voltage (V

IN

) at any pin exceeds the power supplies (V

IN

k

GND or V

IN

l

AV

a

or DV

a

) the current at that pln should be limited to 30 mA

The 120 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 30 mA to four

Note 5

The maximum power dissipation must be derated at elevated temperatures and is dictated by T

Jmax

i

JA

and the ambient temperature T

A

The maximum

allowable power dissipation at any temperature is P

D

e

(T

Jmax

b

T

A

) i

JA

or the number given In the Absolute Maximum Ratings whichever is lower For this

device T

Jmax

e

150 C The typical thermal resistance (i

JA

) of these Paris when board mounted can be found in the following table

Part Number

Thermal Resistance

Package Type

ADC10731CIN

82 C W

N16E

ADC10731CIWM

90 C W

M16B

ADC10732CIN

47 C W

N20A

ADC10732CIWM

80 C W

M20B

ADC10734CIMSA

134 C W

MSA20

ADC10734CIN

47 C W

N20A

ADC10734CIWM

80 C W

M20B

ADC10738CIN

60 C W

N24A

ADC10738CIWM

75 C W

M24B

Note 6

The human body model is a 100 pF capacitor discharged through a 1 5 kX resistor into each pin The machine model is a 200 pF capacitor discharged

directly into each pin

Note 7

See AN-450 ‘‘Surface Mounting Methods and Their Effect on Product Reliability’’ or the section titied ‘‘Surtace Mount’’ found in any post 1986 National

Semiconductor Linear Data Book for other methods of soldering surtace mount devices

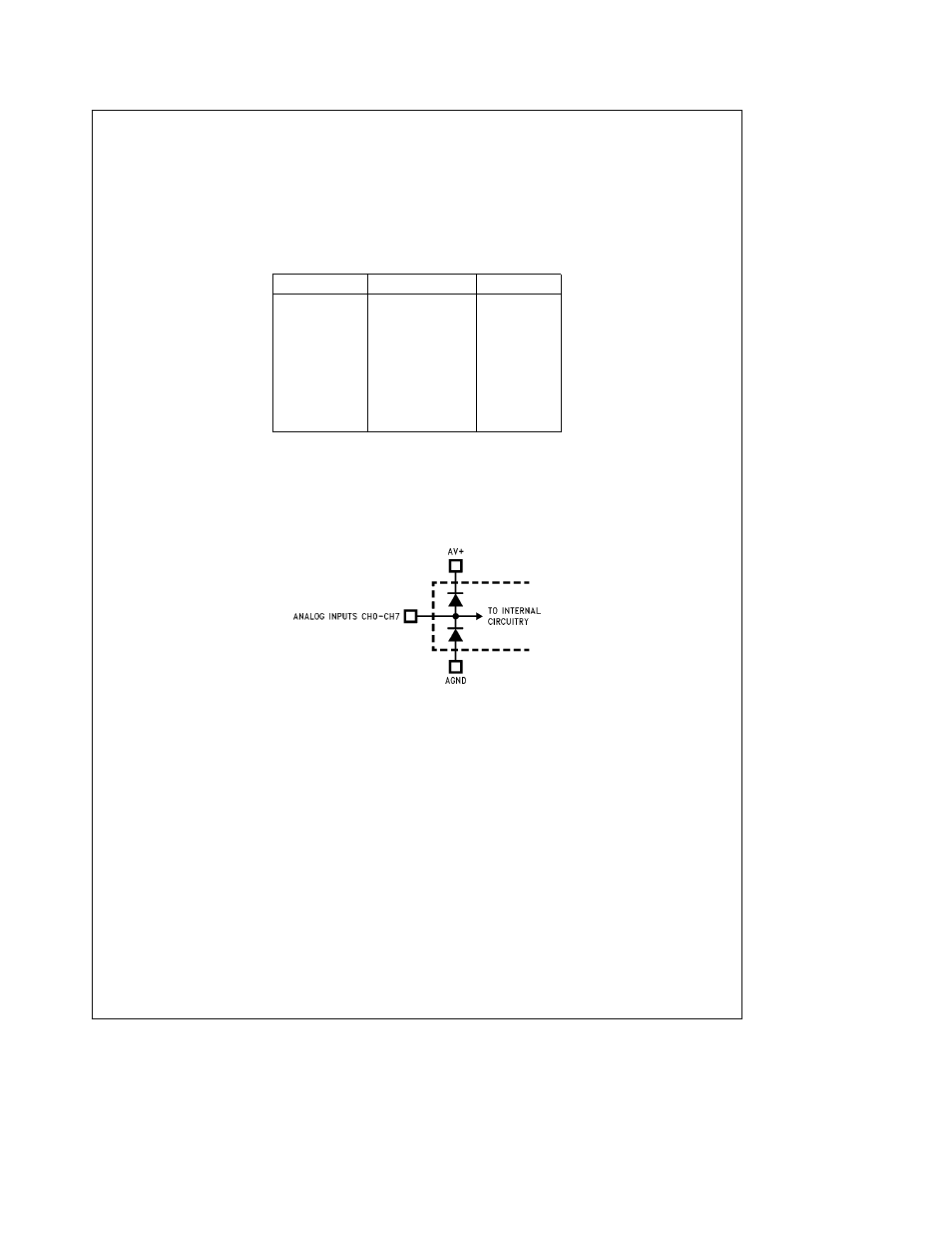

Note 8

Two on-ohip diodes are tied to each analog input as shown below They will forward-conduct for analog input voltages one diode drop below ground or one

diode drop greater than V

a

supply Be careful during testing at low V

a

levels (

a

4 5V) as high level analog inputs (

a

5V) can cause an input diode to conduct

especially at elevated temperatures which will cause errors In the conversion result The specification allows 50 mV forward bias of either diode this means that as

long as the analog V

IN

does not exceed the supply voltage by more than 50 mV the output code will be oorrect Exceeding this range on an unselected channel will

corrupt the reading of a selected channel If AV

a

and DV

a

are minimum (4 5 V

DC

) and full scale must be

s a

4 55 V

DC

TL H 11390 – 6

Note 9

No connection exists between AV

a

and DV

a

on the chip

To guarantee accuracy it is required that the AV

a

and DV

a

be connected together to a power supply with separate bypass filter at eacn V

a

pin

Note 10

One LSB is referenced to 10 bits of resolution

Note 11

Typicals are at T

J

e

T

A

e

25 C and represent most likely pararmetric norm

Note 12

Tested limits are guaranteed to National’s AOQL (Average Outgolng Quality Level)

Note 13

Total unadjusted error includes offset full-scale linearity multiplexer and hold step errors

Note 14

The DC common-mode error is measured in the differential multiplexer mode with the assigned positive and negative input channels shorted together

Note 15

Channel leakage current is measured after the channel selection

Note 16

All the timing specifications are tested at the TTL logic levels V

IL

e

0 8V for a falling edge and V

IH

e

2 0V for a rising TRl-STATE voltage level is forced

to 1 4V

Note 17

The voltage applied to the digital inputs will affect the current drain during power down These devices are tested with CMOS logic levels (logic Low

e

0V

and logic High

e

5V) TTL levels increase the current during power down to about 300 mA

8