5 schematic, Schematic 1-7 introduction – Texas Instruments SLVU013 User Manual

Page 15

Schematic

1-7

Introduction

1.5

Schematic

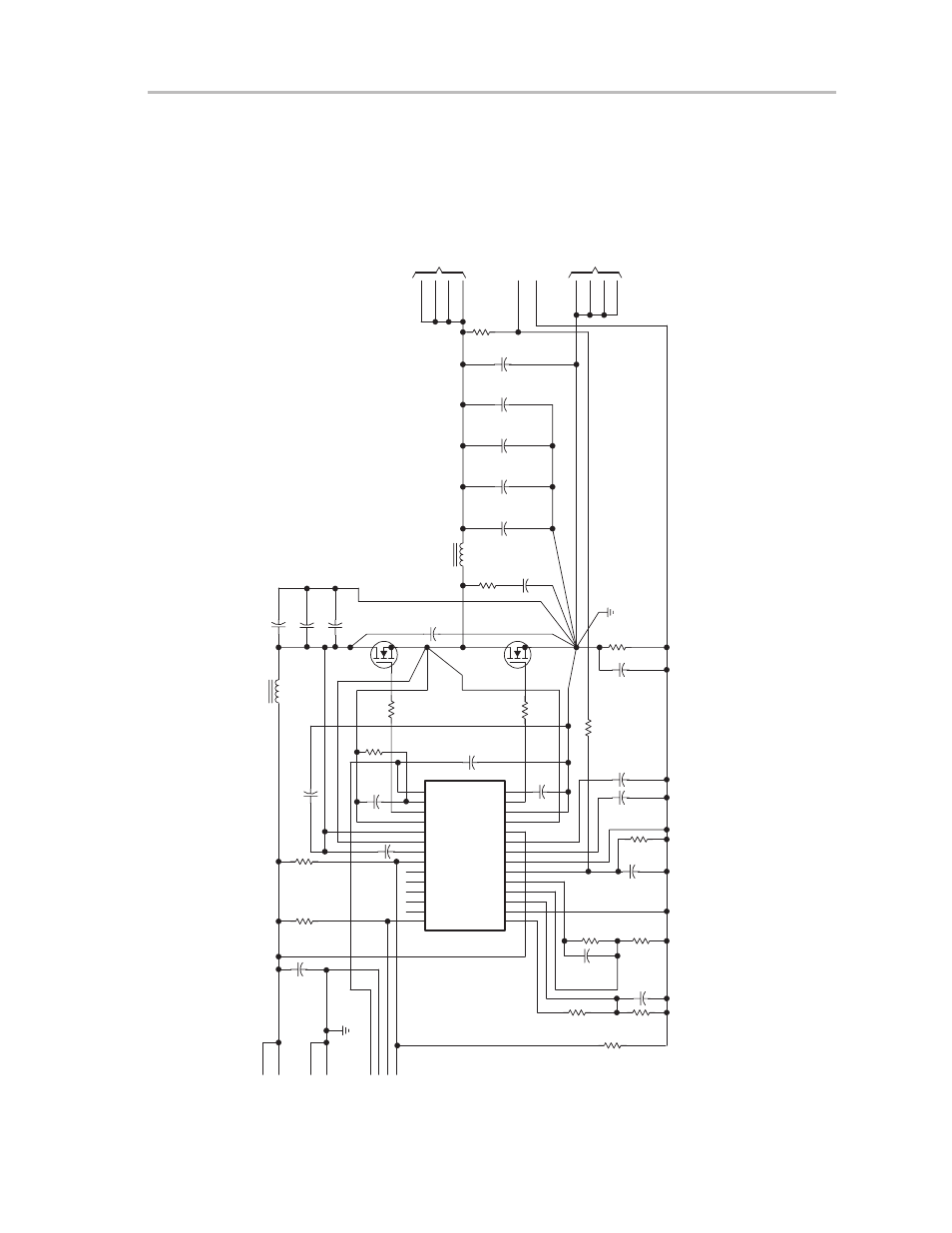

Figure 1–3 shows the EVM converter schematic diagram. The schematic

diagrams for the other EVM converters are identical except for the controller

IC used.

Figure 1–3. SLVP111–114 EVM Converter Schematic Diagram

IOUT

AGND2

OCP

VHYST

VREFB

VSENSE

ANAGND

SLOWST

BIAS

LODRV

LOHIB

DRVGND

LOWDR

DRV

PWRGD

NC

NC

NC

NC

NC

INHIBIT

IOUTLO

LOSENSE

HISENSE

BOOTLO

HUGHDR

BOOT

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

C16

1

µ

F

C8

1

µ

F

R15

1 M

C7

1

µ

F

R3

10

Ω

Q2

Si4410

R4

10

Ω

C6

0.1

µ

F

U1

TPS5633 (See Note)

C5

0.1

µ

F

R2

10 k

Ω

R1

1 k

Ω

+

C1

33

µ

F

10 V

L1

2.2

µ

H

+

C2

150

µ

F

6.3 V

+

C3

150

µ

F

6.3 V

+

C4

150

µ

F

6.3 V

Q1

Si4410

C9

2.2

µ

F

R5

2.7

Ω

C15

0.01

µ

F

L2

1.5

µ

H

+

C10

150

µ

F

4 V

+

C1

1

150

µ

F

+

C12

150

µ

F

+

C13

150

µ

F

C14

10

µ

F

R6

4.7

Ω

J1–18

J1–17

J1–16

J1–15

SL

VP1

1

1

= 3.3 V

SL

VP1

12 = 2.5 V

SL

VP1

13 = 1.8 V

SL

VP1

14 = 1.5 V

O

V

J1–4

J1–2

J1–1

1

J1–14

J1–13

J1–12

PWR

GND

SENSEH

V

SENSEL/

V

ANAGND

R12

4.7

Ω

C18

0.1

µ

F

R8

100

Ω

1%

C22

1

µ

F

C21

0.1

µ

F

R1

1

20 k

Ω

1%

C20

1000 pF

R10

100

Ω

1%

C17

0.1

µ

F

R10

1%

20 k

Ω

C19

0.01

µ

F

R13

750

Ω

R7

1 k

Ω

R9

11

k

Ω

J1–5

J1–6

J1–9

J1–10

J1–7

J1–8

J1–3

J1–1

V

I

RETURN

12 V

RETURN

PG

INHIBIT

NOTE:

Last two digits of U1 indicates output voltage option

TPS5633 = 3.3 V (SL

VP1

1

1

)

TPS5625 = 2.5 V (SL

VP1

12)

TPS5618 = 1.8 V (SL

VP1

13)

TPS5618 = 1.5 V (SL

VP1

14)