Input output signal specificatoins – Toshiba IK-TF5 User Manual

Page 32

32

8. INPUT OUTPUT SIGNAL SPECIFICATOINS

4.5V

HD

VD

0V

4.5V

0V

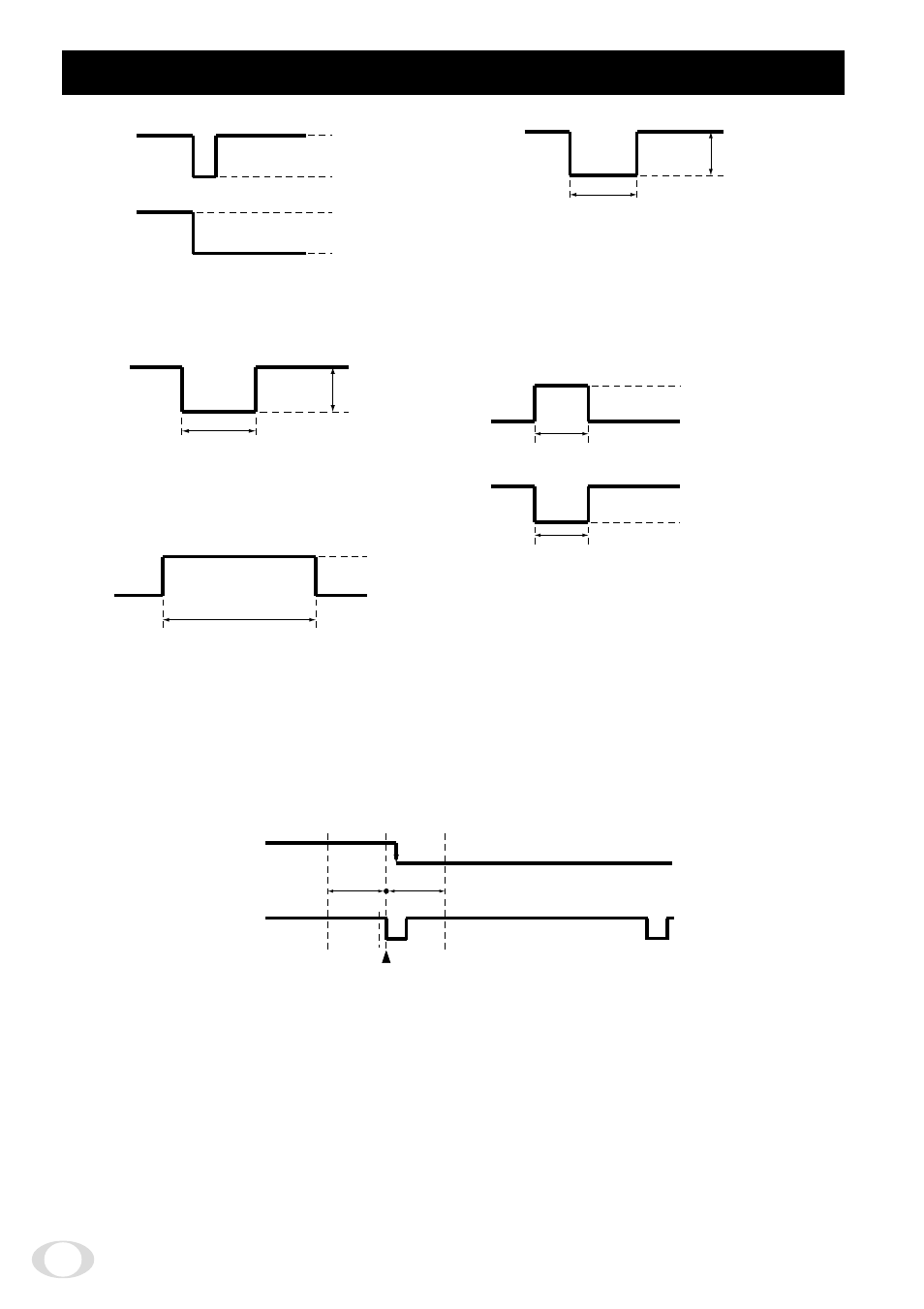

( 1 ) HD/VD Output Amplitude Specifications

( 4 ) HD Input Specifications

The amplitude level is the representative value when ter-

minated with 10k

Ω

. Output is enabled when the rear panel

HD/VD signal input/output switch is set to the INT side.

( 2 ) VIDEO INDEX Output Specifications

The amplitude level is the representative value when ter-

minated with 10k

Ω

.

( 3 ) VD Input Specifications

2.0

µ

s to 5.0

µ

s

2.0

5.0 V(p-p)

* Input impedance: 75W or 1k

Ω

or greater

* Input amplitude 2.0 to 5.0 V(p-p) (75

Ω

termination ON

or OFF)

* Voltage and pulse width were measured at pin 7 of the

12-pin connector located on the rear panel.

4.5V

0V

525H (Partial scanning OFF)

175H (Partial scanning ON)

* Input impedance: 75

Ω

or 10k

Ω

or greater

* Input amplitude 2.0 to 5.0 Vp-p (75

Ω

termination ON

or OFF)

* Voltage and pulse width were measured at pin 6 of

the 12-pin connector located on the rear panel.

( 5 ) Trigger Pulse Specifications

2

5.0V

0

0.4V

(Positive polarity mode)

2

5.0V

0

0.4V

(Negative polarity mode)

More than 2

µ

s

More than 2

µ

s

5H to 21H

2.0 to

5.0 V(p-p)

* Input impedance: 10k

Ω

or greater

* Voltage and pulse width were measured at pin 11

of the 12-pin connector located on the rear panel.

( 6 ) External HD/VD Input Phase Specifications

100

100

External HD

rising edge

Center

Unit : Clock

1 clk=40.74 nsec

External HD

The phase relationship of the external HD and VD should correspond to the center phase (i.e., the external HD falling

edge) as illustrated in the above diagram.

External VD falling edge:

Please input within about 100 clock cycles of the standard center phase.

Note that V sync of the video is output with a delay of about 1H from the external VD at the time of reset-restart and

the external trigger mode.

In the normal mode:

Continuously with the HD period of 31.78 ms and VD period of 16.68 ms (partial scanning ON: 5.56 ms).

Phase timing is as illustrated in the above diagram (with only the falling edge applicable).

In the reset-restart/external trigger mode:

Continuously with the HD period of 31.78 ms. VD (reset) is at an arbitrary timing with the phase of HD being within the

standard of the above diagram.