Sh7211 group – Renesas SH7211 User Manual

Page 8

SH7211 Group

Data Transfer between On-chip RAM Areas with DMAC (Cycle-Stealing Mode)

REJ06B0732-0100/Rev.1.00

March 2008

Page 8 of 13

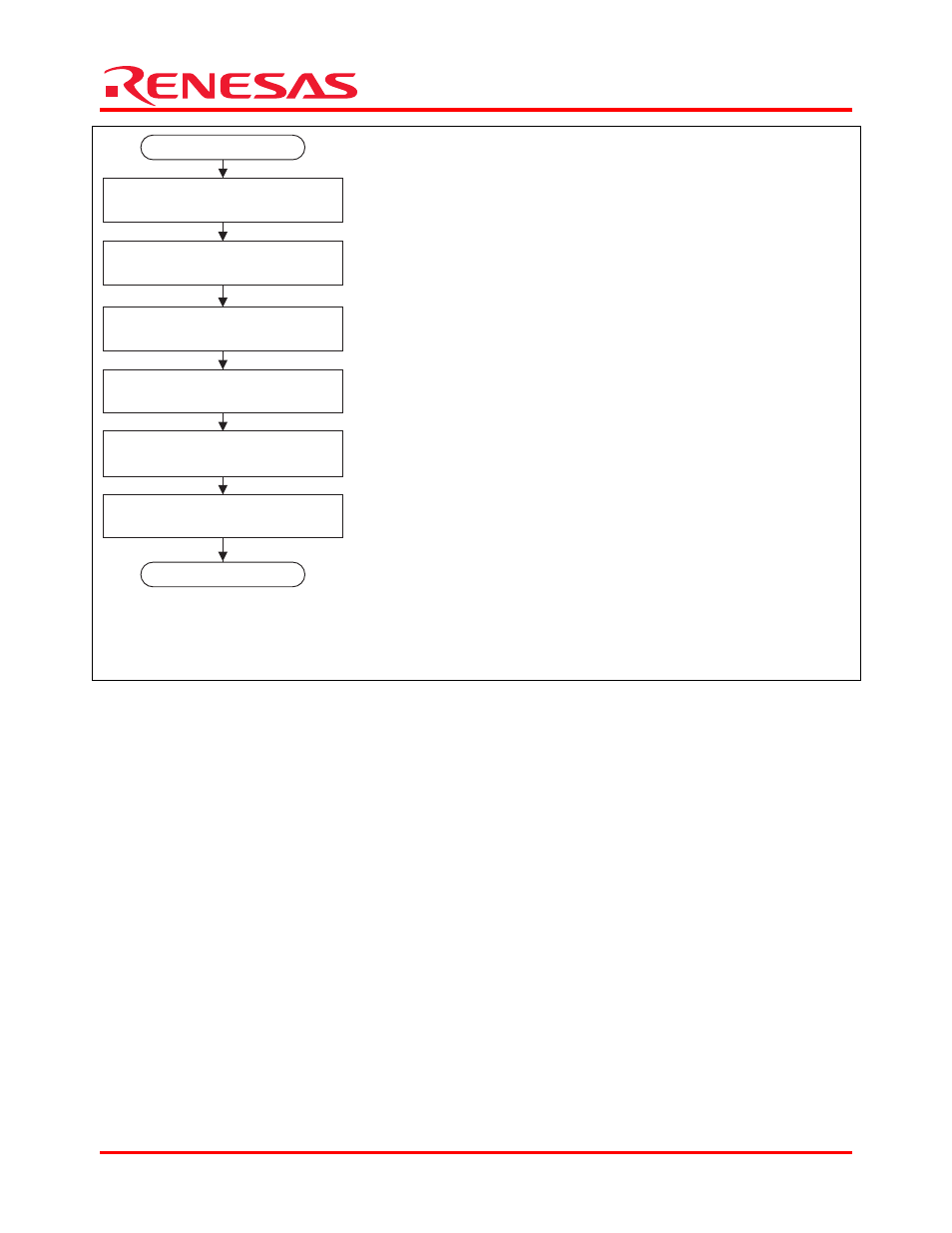

DMAC_init

END

[3]

[4]

[5]

[6]

[1]

[2]

[1] Disable DMA transfer

Set the DE (DMA enable) bit to 0

Disable DMA transfer

[2] Set the DMA transfer source address (SAR_0)

Specify the DMA transfer source address

[3] Set the DMA transfer destination address (DAR_0)

Specify the DMA transfer destination address

[4] Specify the DMA transfer count (DMATCR_0)

Set the DMA transfer count to 128

[5] Set the channel control register (CHCR_0)

Set TC to B’1: transfer data for the count specified in DMATCR

Set RLD to B’0: disable the reload function

Set RS[3:0] (resource selector) to B’0100: auto request

Set DM[1:0] to B’01: increment the destination address

Set SM[1:0] to B’00: fix the source address

Set TB to B’0: cycle steal mode

Set IE to B’0: disable interrupts

[6] Set the DMA operation register (DMAOR)

Read from the AE and MNIF bits and clear them to 0

Clear the address error flag

Set the DME bit to 1 after clearing the flags

Enable DMA transfer on all the channels

Set DMA channel control register

(CHCR_0)

Set DMA source address register

(SAR_0)

Set DMA destination address

register (DAR_0)

Set DMA transfer count register

(DMATCR_0)

Set DMA channel control register

(CHCR_0)

Set DMA operation register

(DMAOR)

Figure 6 Flowchart of Initializing DMAC