3 direct memory access controller (dmac) – Renesas SH7211 User Manual

Page 10

SH7211 Group

Data Transfer between On-chip RAM Areas with DMAC (Cycle-Stealing Mode)

REJ06B0732-0100/Rev.1.00

March 2008

Page 10 of 13

2.4.3

Direct Memory Access Controller (DMAC)

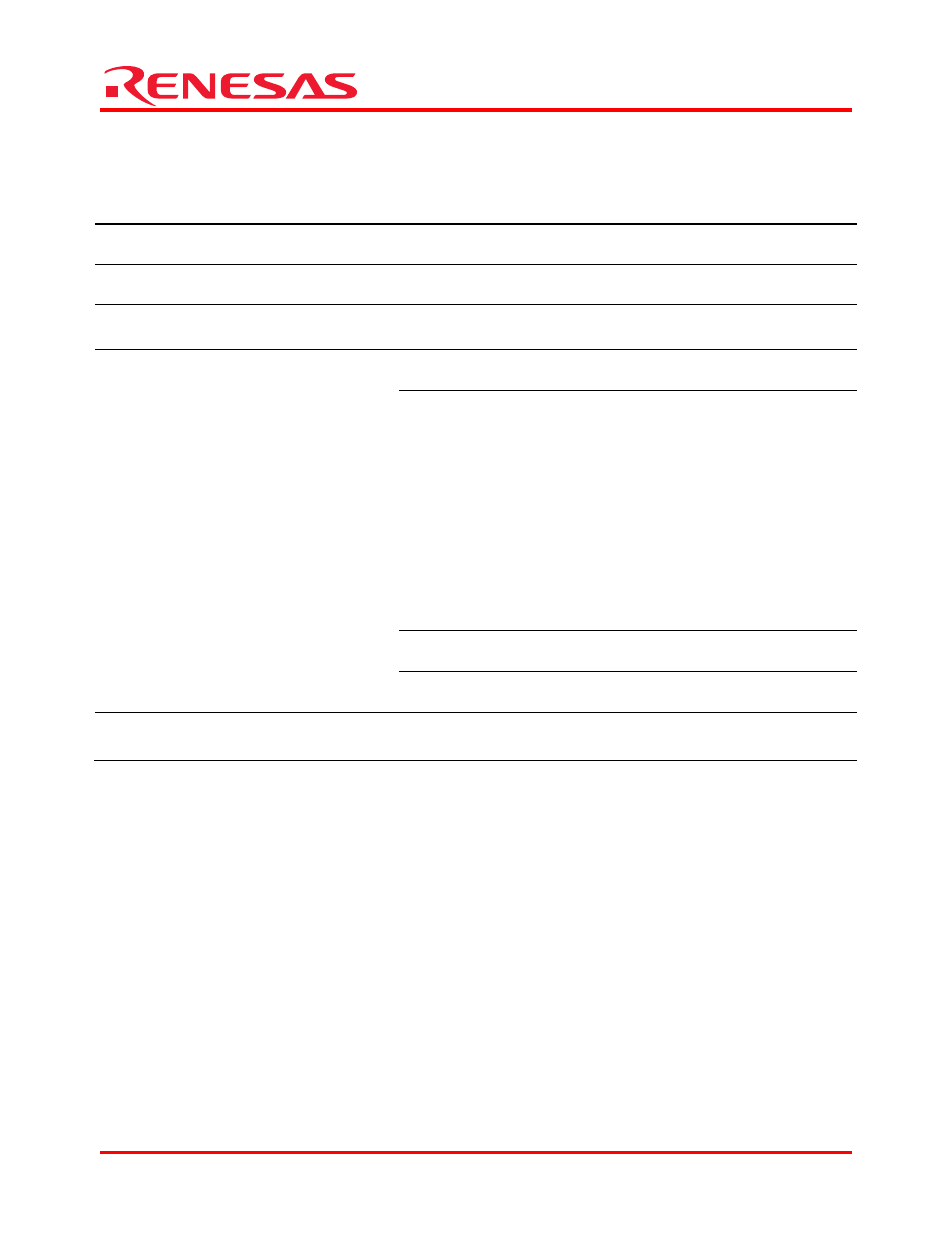

The settings of DMAC registers for the sample program are described in table 7.

Table 7 Settings of DMAC Registers

Register Name

Address

Setting Value

Description

DMA source address

register 0 (SAR)

H’FFFE1000

H’FFF81000

Transfer source start address

DMA destination address

register 0 (DAR)

H’FFFE1004 H’FFF82000 Transfer destination start address

DMA transfer count

register 0 (DMATCR)

H’FFFE1008

D’128

DMA transfer count:

128 transfers

H’0000 0000

Before DMA initialization

DE = “B’0”: disables DMA transfer

H’8000 4410

DMA initialization

TC = “B’1”: transfers data for the count

specified in DMATCR for each transfer

request

DM[1:0] = “B’01”: increments the destination

address

SM[1:0] = “B’00”: fixes the source address

RS[3:0] = “B’0100”: auto request

TB = “B’0”: cycle-stealing mode

TS[1:0] = “B’10”: longword (4 bytes) unit

IE = “B’0”: disables interrupt requests

DE = “B’0”: disables DMA transfer

H’8000 4411

When enabling DMA transfer

DE = “B’1”: enables DMA transfer

DMA channel control

register 0 (CHCR)

H’FFFE100C

H’8000 4410

When disabling DMA transfer

DE = “B’0”: disables DMA transfer

DMA operation register

(DMAOR)

H’FFFE1200 H’0000

0001 DME = “B’1”: enables DMA transfer on all the

channels