Appendix 3.2 pipeline basic operation, Appendices, Appendix 3 – Renesas M32R-FPU User Manual

Page 168: Appendices-10, Appendix 3 pipeline processing

APPENDICES

APPENDICES-10

M32R-FPU Software Manual (Rev.1.01)

Appendix Figure 3.2.1 Pipeline Flow with no Stall (1)

Appendix 3.2 Pipeline Basic Operation

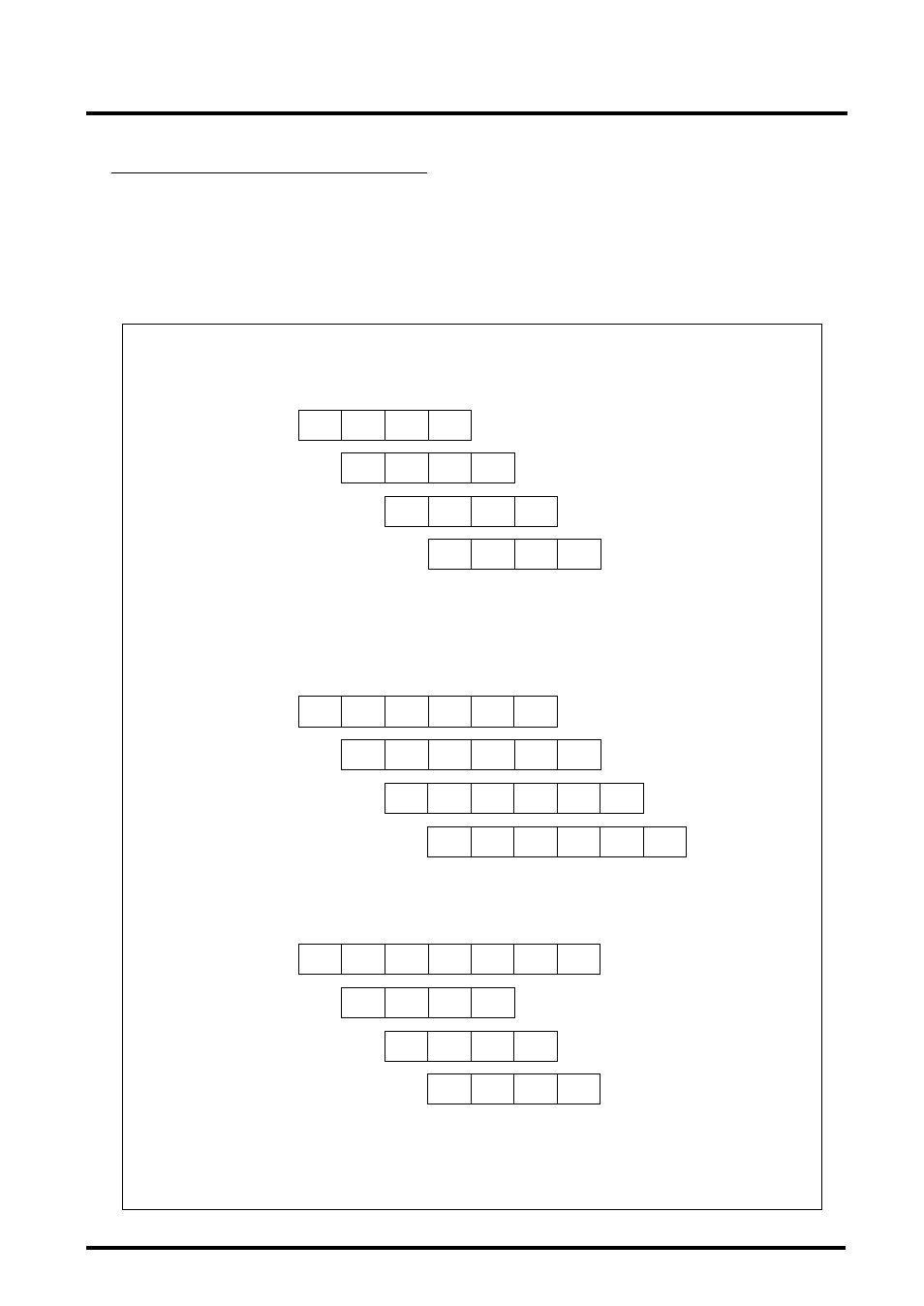

(1) Pipeline Flow with no Stall

The following diagram shows an ideal pipeline flow that has no stall and executes each

instruction in 1 clock cycle. (Since this is just an ideal case, all instructions may not be

piplined in.)

APPENDIX 3

Appendix 3 Pipeline Processing

IF

D

E

WB

IF

D

WB

E

D

WB

E

IF

D

WB

E

IF

D

E

WB

ST R0,@-R15

ST R1,@-R15

LDI R0,#1

ADD R0,R1

OR R0,R2

CMP R0,R3

IF

D

WB

MEM2

MEM1 MEM2

E

MEM1

IF

D

E

WB

LD R2,@R15+

LD R3,@R15+

IF

D

WB

MEM2

MEM1 MEM2

E

MEM1

IF

D

E

WB

LD R0,@R2

LDI R1,#1

IF

D

WB

MEM1 MEM1 MEM2

E

IF

D

E

WB

ADD R1,R3

OR R1,R4

IF

D

WB

E

a load/store instruction (out-of-order-completion)

IF

* A multi-cycle instruction, such as multiply or divide, executes

multiple cycles in the E stage.

* A multi-cycle instruction, such as multiply or divide, executes multiple

cycles in the E stage.