Mulwlo, Multiply word and low-order halfword, Instructions – Renesas M32R-FPU User Manual

Page 115

3

3-77

M32R-FPU Software Manual (Rev.1.01)

MULWLO

MULWLO

DSP fucntion instruction

Multiply

word and low-order halfword

[Mnemonic]

MULWLO Rsrc1,Rsrc2

[Function]

Multiply

accumulator = ( ( signed ) Rsrc1 * ( signed short ) Rsrc2 );

[Description]

MULWLO multiplies the 32 bits of Rsrc1 and the low-order 16 bits of Rsrc2, and stores the

result in the accumulator.

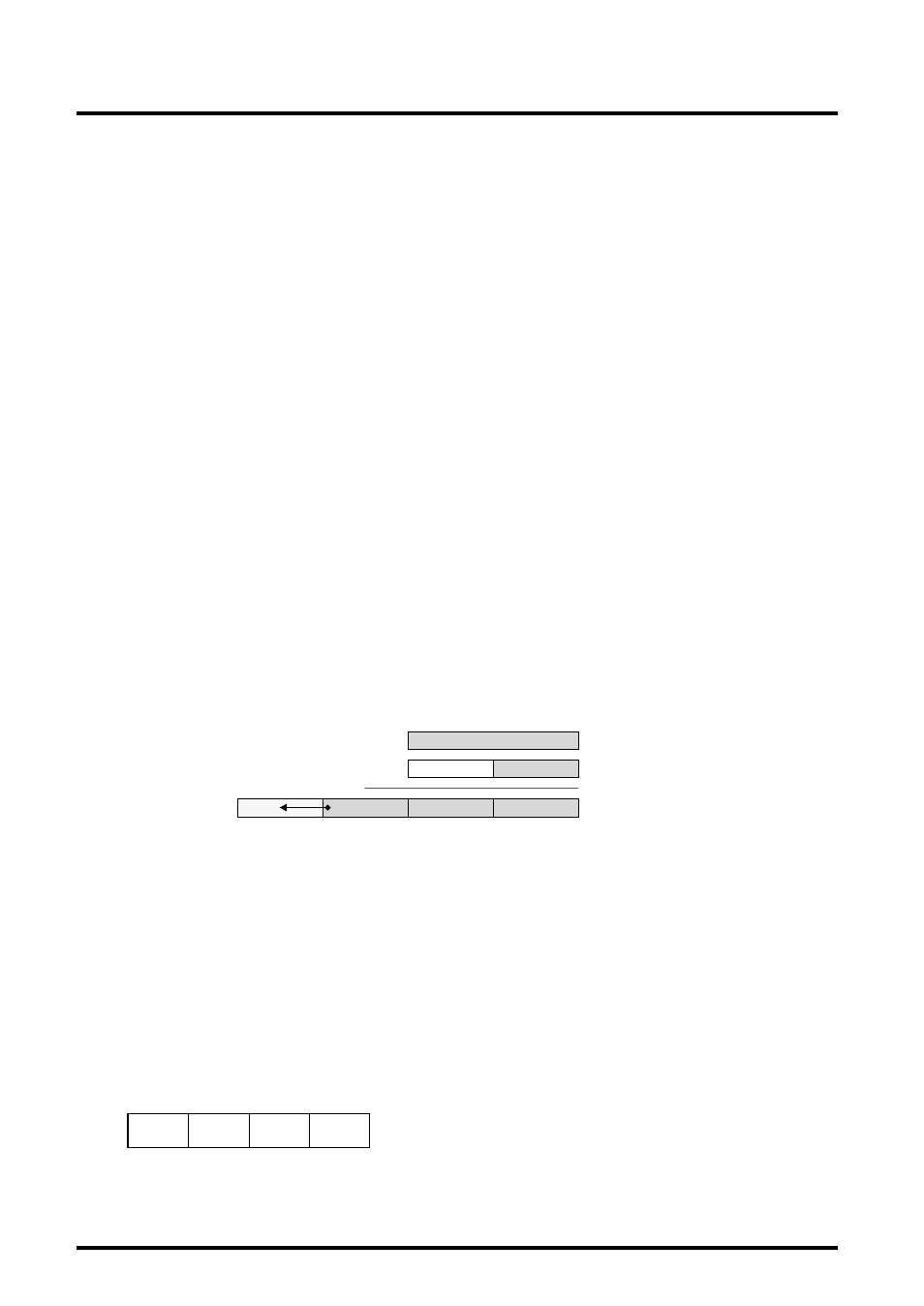

The LSB of the multiplication result is aligned with the LSB of the accumulator, and the portion

corresponding to bits 0 through 15 of the accumulator is sign extended. The 32 bits of Rsrc1 and

low-order 16 bits of Rsrc2 are treated as signed values.

The condition bit (C) is unchanged.

[EIT occurrence]

None

[Encoding]

Rsrc1

Rsrc2

x

0

15 16

31

0

15 16

31 32

47 48

63

Value in accumulator after the

execution of the MULWLO instruction

Sign extension

low-order 16 bits

32 bits

src1

0011

MULWLO Rsrc1,Rsrc2

src2

0011

INSTRUCTIONS

3.2 Instruction description