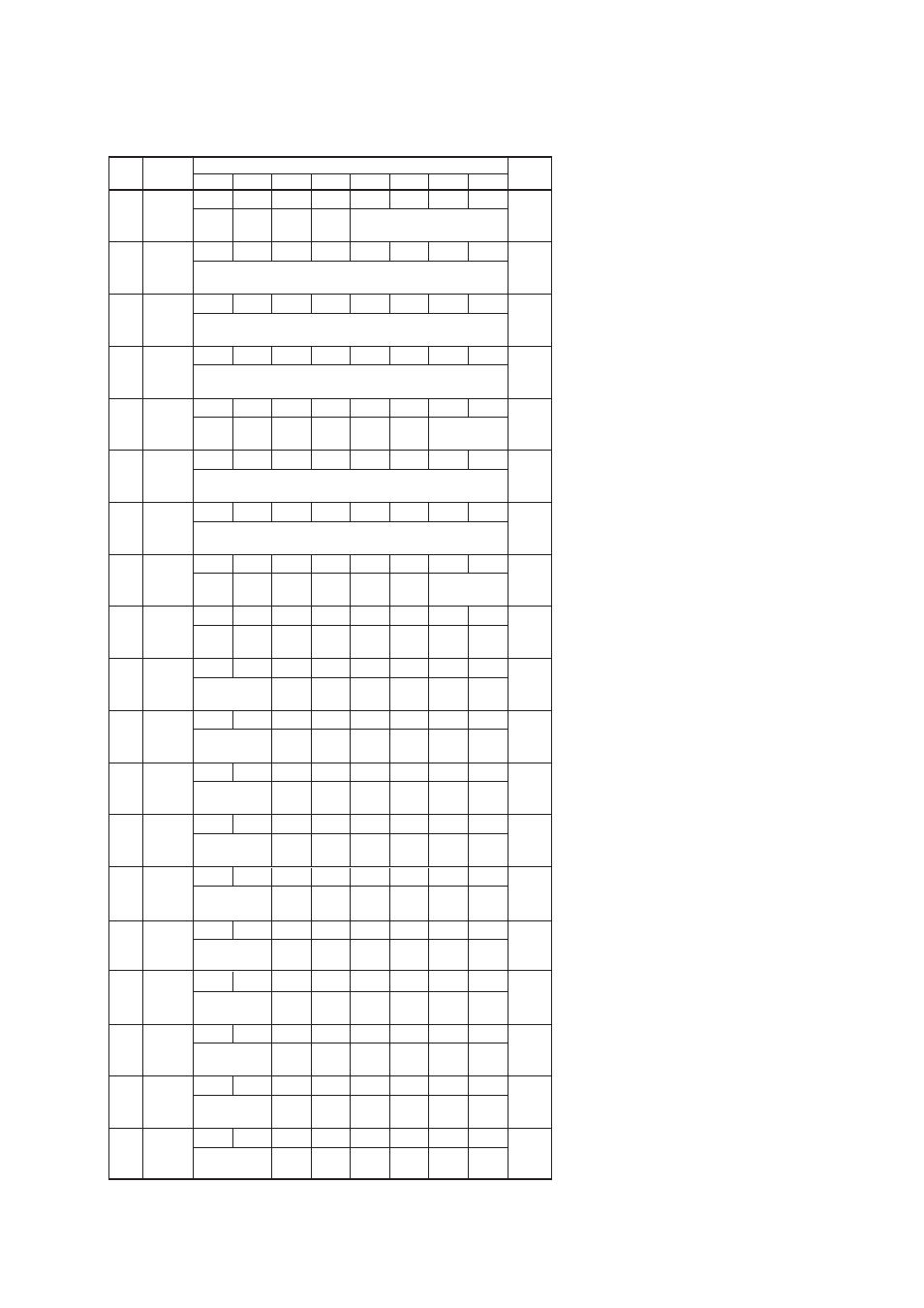

Xvii - 13 – Panasonic MN101C77C User Manual

Page 513

XVII - 13

Chapter 17 Appendices

Special Function Registers List

X'3FD1'

-

-

-

BTSTP

AT1IR3

AT1IR2

AT1IR1

AT1IR0

ATCNT1

Burst Transfer

Enable flag

ATC1 Activation Factor Selection

XIV - 7

X'3FD2'

X'3FD3'

X'3FD4'

X'3FD5'

AT1TRC7

AT1TRC6

AT1TRC5

AT1TRC4

AT1TRC3

AT1TRC2

AT1TRC1

AT1TRC0

X'3FD6'

AT1TRC

ATC1 Transfer Count Setting

XIV - 7

AT1MAP0L7 AT1MAP0L6 AT1MAP0L5 AT1MAP0L4 AT1MAP0L3 AT1MAP0L2 AT1MAP0L1 AT1MAP0L0

X'3FD7'

AT1MAP0L

ATC1 Memory Pointer 0 Lower 8 bits

XIV - 8

AT1MAP0M15 AT1MAP0M14 AT1MAP0M13 AT1MAP0M12 AT1MAP0M11 AT1MAP0M10 AT1MAP0M9 AT1MAP0M8

X'3FD8'

AT1MAP0M

ATC1 Memory Pointer 0 Middle 8 bits

XIV - 8

-

-

-

-

-

-

AT1MAP0H17 AT1MAP0H16

X'3FE1'

AT1MAP0H

ATC1 Memory Pointer 0

Upper 2 bits

XIV - 8

AT1MAP1L7 AT1MAP1L6 AT1MAP1L5 AT1MAP1L4 AT1MAP1L3 AT1MAP1L2 AT1MAP1L1 AT1MAP1L0

X'3FE2'

AT1MAP1L

ATC1 Memory Pointer 1 Lower 8 bits

XIV - 8

AT1MAP1L15 AT1MAP1L14 AT1MAP1M13 AT1MAP1M12 AT1MAP1M11 AT1MAP1M10 AT1MAP1M9 AT1MAP1M8

X'3FE3'

AT1MAP1M

ATC1 Memory Pointer 1 Middle 8 bits

XIV - 8

-

-

-

-

-

-

AT1MAP1H17 AT1MAP1H16

X'3FE4'

AT1MAP1H

ATC1 Memory Pointer 1

Upper 2 bits

XIV - 8

-

-

-

-

-

PIR

WDIR

RESERVED

NMICR

Program

Interrupt

Request

III - 16

Set Always

to "0"

Watchdog Timer

Interrupt

Request

IRQ0LV1

IRQ0LV0

REDG0

-

-

-

IRQ0IE

IRQ0IR

IRQ0ICR

Request IRQ0

Interrupt

III - 17

Enable IRQ0

Interrupt

IRQ0 Interrupt

Valid Edge

Specify IRQ0

Interrupt Level

IRQ1LV1

IRQ1LV0

REDG1

-

-

-

IRQ1IE

IRQ1IR

IRQ1ICR

Request IRQ1

Interrupt

III - 18

Enable IRQ1

Interrupt

IRQ1 Interrupt

Valid Edge

Specify IRQ1

Interrupt Level

IRQ2LV1

IRQ2LV0

REDG2

-

-

-

IRQ2IE

IRQ2IR

IRQ2ICR

Request IRQ2

Interrupt

III - 19

Enable IRQ2

Interrupt

IRQ2 Interrupt

Valid Edge

Specify IRQ2

Interrupt Level

Bit Symbol /Initial Value /Description

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Address

Register

Page

X'3FE5'

X'3FE6'

IRQ3LV1

IRQ3LV0

REDG3

-

IRQ3IE

IRQ3IR

IRQ3ICR

Request IRQ3

Interrupt

III - 20

Enable IRQ3

Interrupt

IRQ3 Interrupt

Valid Edge

Specify IRQ3

Interrupt Level

IRQ4LV1

IRQ4LV0

REDG4

-

IRQ4IE

IRQ4IR

IRQ4ICR

Request IRQ4

Interrupt

III - 21

Enable IRQ4

Interrupt

IRQ4 Interrupt

Valid Edge

Specify IRQ4

Interrupt Level

-

-

-

-

X'3FED'

X'3FEF'

TM4LV1

TM4LV0

-

TM4IE

TM4IR

TM4ICR

Request TM4

Interrupt

III - 24

Enable TM4

Interrupt

Specify TM4

Interrupt Level

TM6LV1

TM6LV0

-

TM6IE

TM6IR

Request TM6

Interrupt

III - 26

Enable TM6

Interrupt

Specify TM6

Interrupt Level

TM6ICR

X'3FEA'

TM1LV1

TM1LV0

-

TM1IE

TM1IR

Request TM1

Interrupt

III - 23

Enable TM1

Interrupt

Specify TM1

Interrupt Level

TM1ICR

-

-

-

-

-

-

-

X'3FEE'

TM5LV1

TM5LV0

-

TM5IE

TM5IR

TM5ICR

Request TM5

Interrupt

III - 25

Enable TM5

Interrupt

Specify TM5

Interrupt Level

-

-

-

-

-

X'3FE9'

TM0LV1

TM0LV0

-

-

-

-

TM0IE

TM0IR

TM0ICR

Request TM0

Interrupt

III - 22

Enable TM0

Interrupt

Specify TM0

Interrupt Level