Panasonic MN101C77C User Manual

Page 102

Chapter 3 Interrupts

III - 8

Overview

■

Determination of Interrupt Acceptance

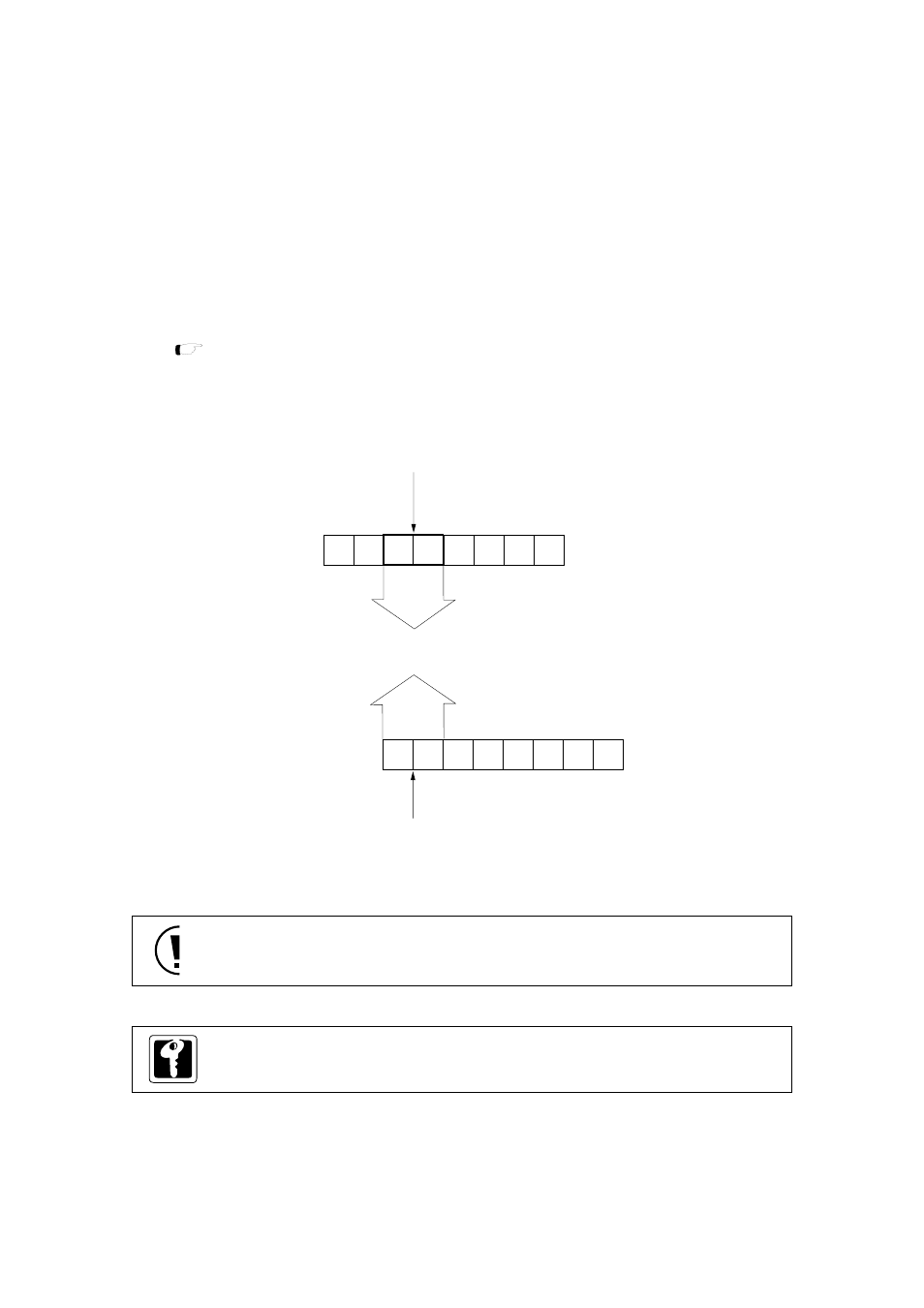

The following is the procedure from interrupt request input to acceptance.

(1)

The interrupt request flag (xxxIR) in the corresponding external interrupt control

register(IRQnICR) or internal interrupt control register (xxxICR) is set to '1'.

(2)

An interrupt request is input to the CPU, If the interrupt enable flag (xxxIE) in the same register

is '1'.

(3)

The interrupt level (IL) is set for each interrupt. The interrupt level (IL) is input to the CPU.

(4)

The interrupt request is accepted, if IL has higher priority than IM and MIE is '1

(5)

After the interrupt is accepted, the hardware resets the interrupt request flag (xxxIR) in the

interrupt control register (xxxICR) to '0'.

Figure 3-1-4 Determination of Interrupt Acceptance

The corresponding interrupt enable flag (xxxIE) is not cleared to "0", even if the interrupt is

accepted.

7

xxxICR

VF

IM1

---

IM0

NF

7

0

PSW

Level judgement. Accepted if IL Current interrupt mask level (IM) Generated interrupt level (IL) xxxIR xxxIE xxxLV1 CF ZF 0 MIE xxxLV0 [ Chapter 2. 2-1-7 Processor Status Word ] When the setting is as xxxLV=1, XXXLV0=1, the interrupt of that vector is disabled, regard- less of the value of xxxIE, xxxIR.