Lakeshore Learning Materials 647 User Manual

Page 33

Lake Shore Model 647 Magnet Power Supply User’s Manual

Remote Operation

4-3

The Status Byte Register consists of a single data byte containing seven bits of MPS status information.

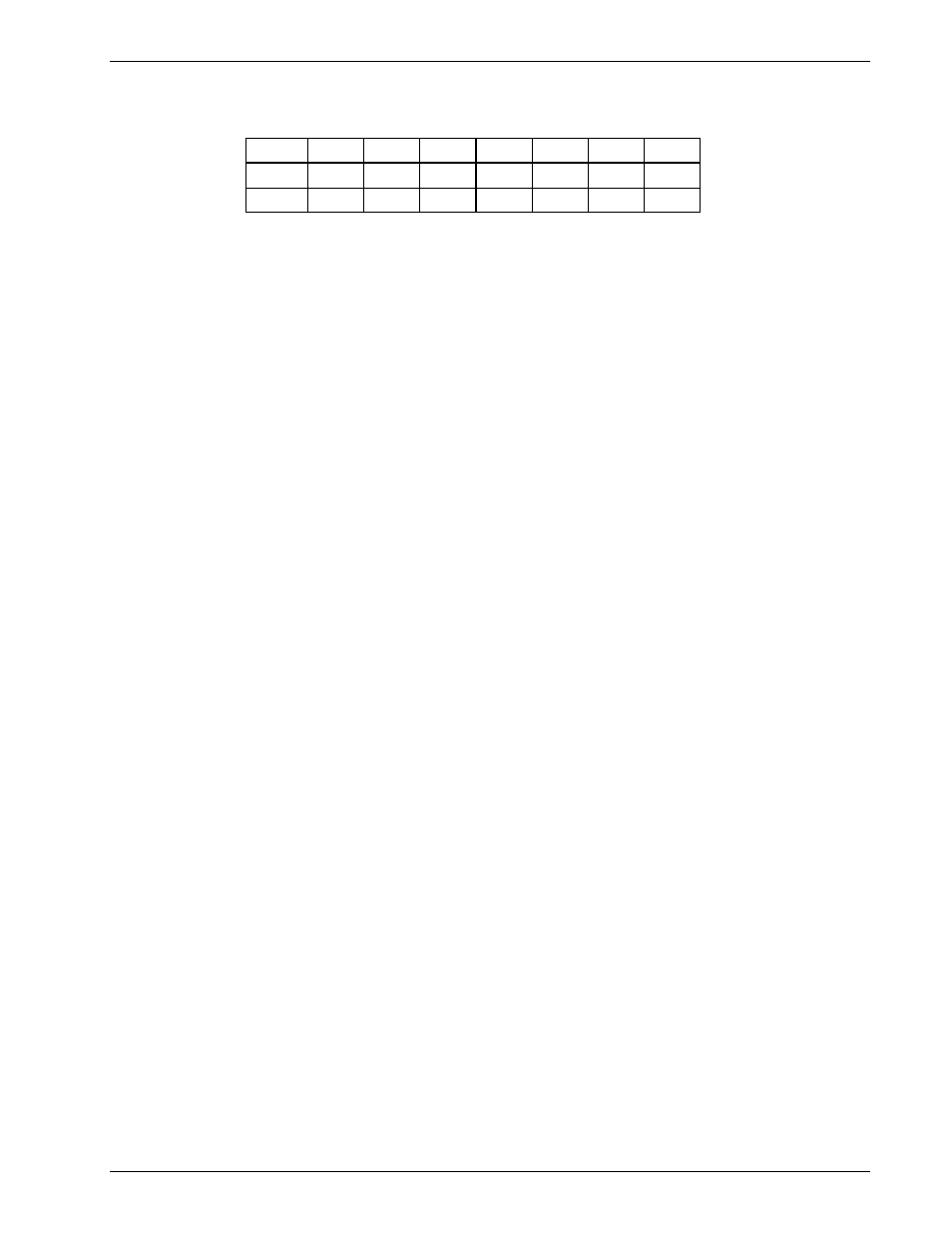

STATUS BYTE REGISTER FORMAT

7 6 5 4 3 2 1 0

Bit

128

64 32 16 8 4 2 1

Weighting

SDR SRQ ESB OVP ERR RSC LIM ODR Bit Name

If the Service Request is enabled, any bits that are set cause the MPS to pull the SRQ management low to

signal the BUS CONTROLLER. These bits reset to zero upon a serial poll of the Status Byte Register.

The Service Request Enable Register inhibits or enables any of the status reports in the Status Byte Register.

The *SRE command sets the bits. A bit that is set enables its function. Inhibit these reports by turning OFF

their corresponding bits in the Service Request Enable Register. Refer to the *SRE discussion.

Setting Data Ready (SDR) Bit (7). When set, the MPS resets current and voltage to 0 A and 1 V because of

OVP or RI activity.

Service Request (SRQ) Bit (6). Determines whether the MPS is to report via the SRQ line and five bits

determine which status reports to make. If bits 0, 1, 2, 3, 4 and/or 5 are set, then the corresponding bit in the

Status Byte Register is set. The MPS produces a service request only if bit 6 of the Service Request Enable

Register is set. If disabled, the Status Byte Register can still be read by the BUS CONTROLLER by means of

a serial poll (SPE) to examine the status reports, but the Service Request does not interrupt the BUS

CONTROLLER. The *STB common command reads the Status Byte Register but does not clear the bits.

Certain bits in the Status Byte Register continually change.

Above are bit assignments in the Status Byte

Register. These reports occur only if the bits are enabled in the Service Request Enable Register.

Event Status (ESB) Bit (5). When set, it indicates if one of the bits from the Standard Event Status Register

has been set. (Refer to Paragraph 4.1.4.2.)

Overvoltage Protection (OVP) Bit (4) Indicates overvoltage (quench) protection circuit activation.

Error (ERR) Bit (3). Indicates operation error. The error displays on the front panel and can be read using the

*TST? Command.

Ramp Segment Complete (RSC) Bit (2). Indicates active ramp segment completion.

Limit Exceeded (LIM) Bit (1). Indicates a new current or voltage exceeds the current or compliance voltage

limit. Read the new setting with the ISET? or VSET? commands.

Output Data Ready (ODR) Bit (0). When set, makes current and voltage readings available.