Emif configuration, Default emif configuration, Description of the pld board registers – Kane Industries C6713CPU User Manual

Page 23: Table 4: ce2 default configuration, Table 5: ce3 default configuration

H

ARDWARE

R

EFERENCE

G

UIDE

MICRO

-

LINE

®

C6713CPU

Date : 28 November 2005

Doc. no. : C6713CPU_HRG

Iss./Rev : 1.1

Page : 23

3.8 EMIF

Configuration

All accesses to off-DSP-chip peripherals, such as on-board SDRAM, the UART or the FPGA are

performed by the DSP's external memory interface (EMIF). The timings and interface type for

these accesses can be software-programmed separately for each CE space (see Table 2 for an

overview of the CE space usage).

3.8.1 Default EMIF configuration

When the C6713CPU is reset or powered on, it automatically boots the Flash File System, which

initializes the EMIF to a safe timing. This timing can be used for many applications, so that no

further EMIF initialization is necessarily required. However, I/O performance can be optimized by

application software by faster accesses to the FPGA and off-board peripherals. This can be done

by modifying the timing settings for the CE2 and CE3 address spaces. Examples for this can be

found in the software examples that are shipped with the C6713CPU.

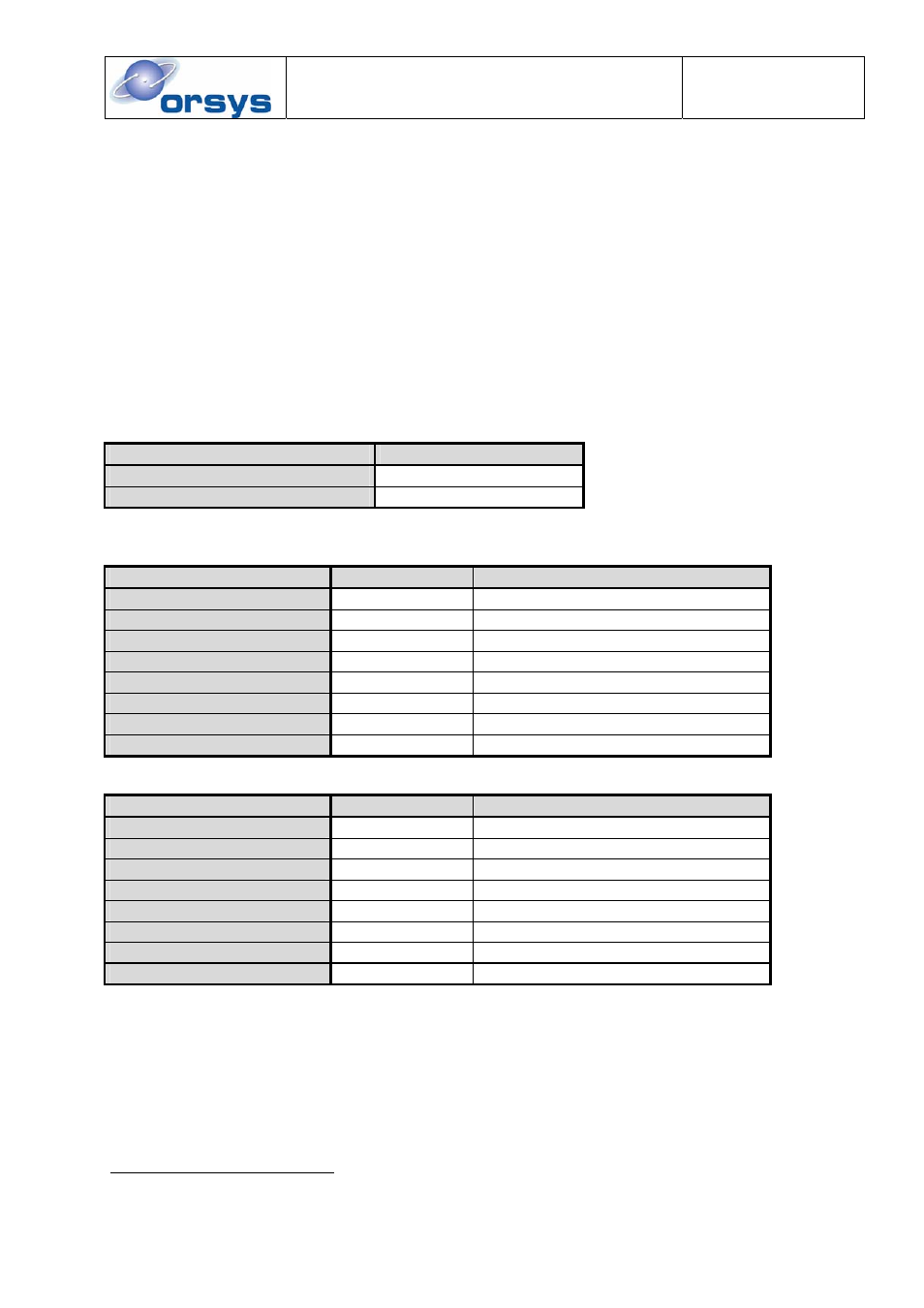

CE space configuration register

32 bit initialization value

CE2 32B3

8A23

CE3 32B3

8A13

Table 3: default initialization values for the FPGA related CE space registers

Parameter

Value

Timing for an EMIF clock of 100MHz

bus width

32 bit

n/a

Read set-up time

3 EMIF clocks

30 ns

Read strobe time

10 EMIF clocks

100 ns

Read hold time

3 EMIF clocks

30 ns

Read/write turnaround time 2 EMIF clocks

20 ns

Write set-up time

3 EMIF clocks

30 ns

Write strobe time

10 EMIF clocks

100 ns

Write hold time

3 EMIF clocks

30 ns

Table 4: CE2 default configuration

Parameter

Value

Timing for an EMIF clock of 90MHz

bus width

16 bit

n/a

Read set-up time

3 EMIF clocks

30 ns

Read strobe time

10 EMIF clocks

100 ns

Read hold time

3 EMIF clocks

30 ns

Read/write turnaround time 2 EMIF clocks

20 ns

Write set-up time

3 EMIF clocks

30 ns

Write strobe time

10 EMIF clocks

100 ns

Write hold time

3 EMIF clocks

30 ns

Table 5: CE3 default configuration

3.9 Description of the PLD Board Registers

The PLD board registers are mapped into the DSP's CE1 address space. Table 6 lists the address

map of all board registers. The register mnemonics are used in this documentation as well as in

the software that is shipped together with the board.

1

These initialization values are only valid for an EMIF clock setting of 90MHz. If another EMIF

clock is used, these settings may be different.