Ddr3l unbuffered dimm ordering information, Key features, Address configuration – Samsung M391B5773DH0 User Manual

Page 4: Datasheet, Ddr3l sdram, Unbuffered dimm

- 4 -

datasheet

DDR3L SDRAM

Rev. 1.0

Unbuffered DIMM

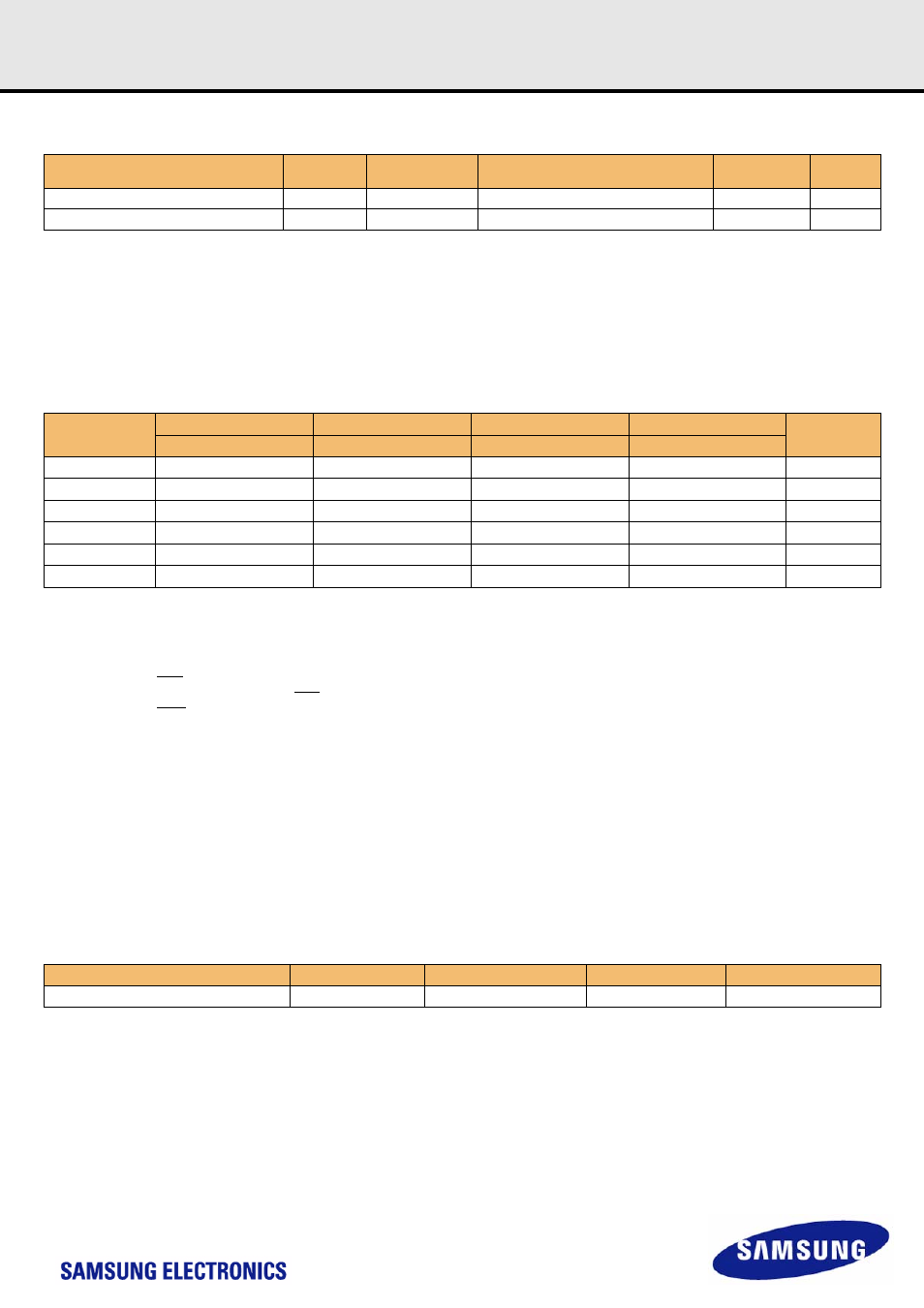

1. DDR3L Unbuffered DIMM Ordering Information

NOTE :

1. "##" - F8/H9/K0

2. F8 - 1066Mbps 7-7-7 / H9 - 1333Mbps 9-9-9 / K0 - 1600Mbps 11-11-11

- DDR3-1600(11-11-11) is backward compatible to DDR3-1333(9-9-9), DDR3-1066(7-7-7)

- DDR3-1333(9-9-9) is backward compatible to DDR3-1066(7-7-7)

2. Key Features

• JEDEC standard 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V) Power Supply

• V

DDQ

= 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V)

• 400MHz f

CK

for 800Mb/sec/pin, 533MHz f

CK

for 1066Mb/sec/pin, 667MHz f

CK

for 1333Mb/sec/pin, 800MHz f

CK

for 1600Mb/sec/pin

• 8 independent internal bank

• Programmable CAS Latency: 6,7,8,9,10,11

• Programmable Additive Latency(Posted CAS) : 0, CL - 2, or CL - 1 clock

• Programmable CAS Write Latency(CWL) = 5 (DDR3-800), 6 (DDR3-1066), 7 (DDR3-1333) and 8 (DDR3-1600)

• Burst Length: 8 (Interleave without any limit, sequential with starting address “000” only), 4 with tCCD = 4 which does not allow seamless read or

write [either On the fly using A12 or MRS]

• Bi-directional Differential Data Strobe

• On Die Termination using ODT pin

• Average Refresh Period 7.8us at lower then T

CASE

85

°C, 3.9us at 85°C < T

CASE

≤ 95°C

• Asynchronous Reset

3. Address Configuration

Part Number

2

Density

Organization

Component Composition

Number of

Rank

Height

M391B5773DH0-YF8/H9/K0

2GB

256Mx64

256Mx8(K4B2G0846D-HY##)*9

1

30mm

M391B5273DH0-YF8/H9/K0

4GB

512Mx72

256Mx8(K4B2G0846D-HY##)*18

2

30mm

Speed

DDR3-800

DDR3-1066

DDR3-1333

DDR3-1600

Unit

6-6-6

7-7-7

9-9-9

11-11-11

tCK(min)

2.5

1.875

1.5

1.25

ns

CAS Latency

6

7

9

11

nCK

tRCD(min)

15

13.125

13.5

13.75

ns

tRP(min)

15

13.125

13.5

13.75

ns

tRAS(min)

37.5

37.5

36

35

ns

tRC(min)

52.5

50.625

49.5

48.75

ns

Organization

Row Address

Column Address

Bank Address

Auto Precharge

256Mx8(2Gb) based Module

A0-A14

A0-A9

BA0-BA2

A10/AP