9] circuit diagram, Block diagram – Sharp AR-PB8 User Manual

Page 24

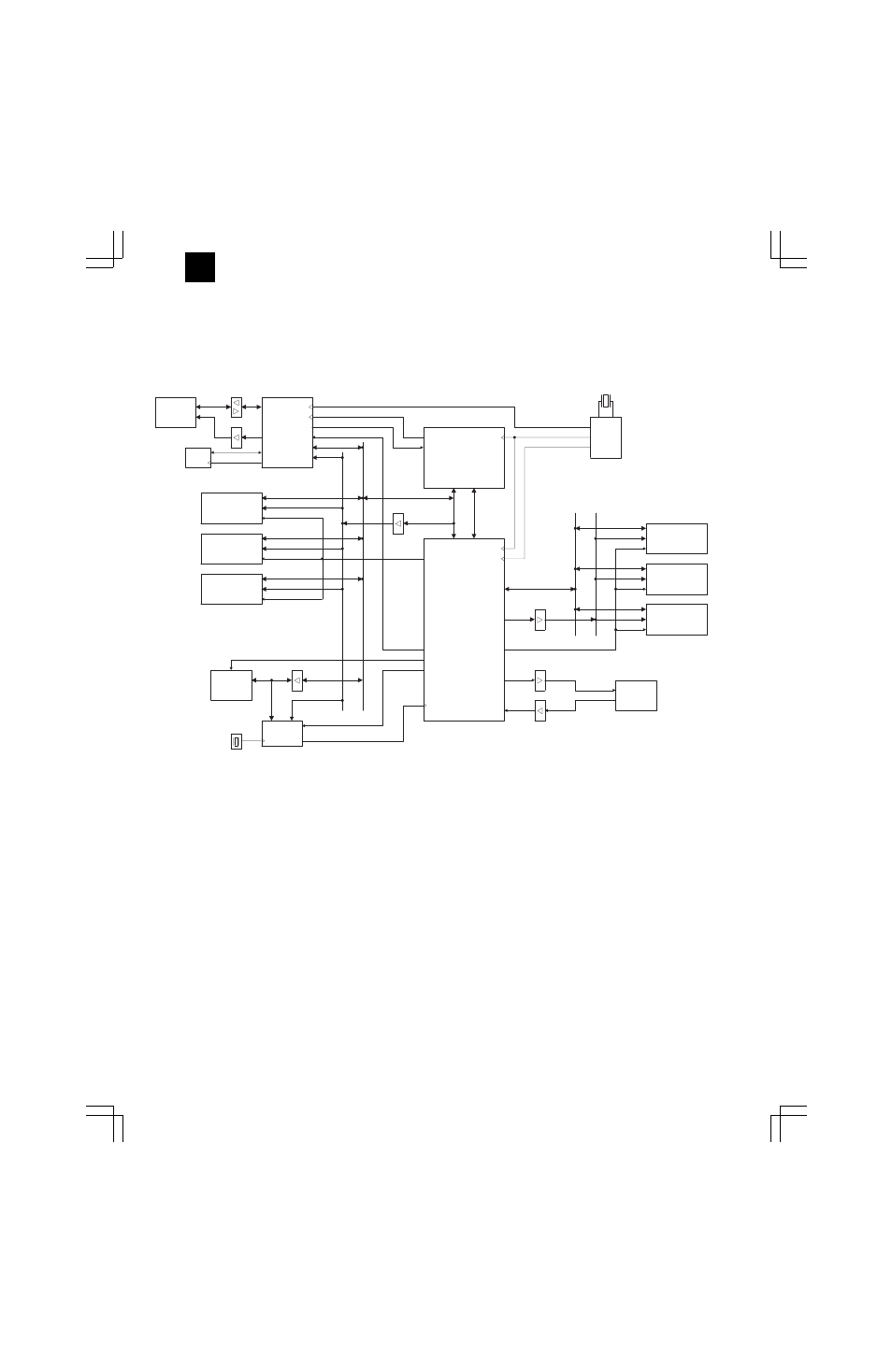

[9] CIRCUIT DIAGRAM

1. BLOCK DIAGRAM

CPU

NR4650

(Internal 133MHz)

G/A (1)

SYSAD[63:0]

SYSCMD[8:0]

SYSAD[31:0]

SYSAD[53:33]

SYSAD[31:0]

RAD[21:1]

RCS_[3:0]

PIACS1_

PIACS0_

MD[63:0]

MA[11:0]

RAM

8MB

RAM

DIMM168 64MB Max

RAM

DIMM168 64MB Max

MD[63:0]

MBA[11:0]

RAS0 CAS[7:0]

Digital copier I/F

CY2292

14.318MHz

44.44MHz

14.318MHz

MASTERCLK

MASTERCLK

SCLK

VFCLK

SYSAD[15:0]

RAD[5:2]

Boot ROM

Code ROM 0

Code ROM 1

DIMM72

Optional

(AR-PS1)

SYSAD[31:0]

RAD[21:0]

RAD[21:0]

RAD[21:0]

SYSAD[31:0]

SYSAD[31:0]

G/A (2)

EEPROM

PARACONN

PDATA[7:0]

SCLK

MODECLK

NETWORKCONN

LDT[15:0]

SYSAD[15:0]

D9001MFH

LDT[7:0]

RAD2

PIACS2_

VFCLK

81.2376MHz

RCS1_

RCS0_

RCS2_

MODEIN

MODEIN

MBRAS1 MBRAS2

RAS0

CAS[7:0]

MBRAS1

CAS[7:0]

MBRAS2

CAS[7:0]

22.22MHz

2MB

2MB

AR-PB8

9 – 1