Camera link interface, Cv-m2, Camera link bit allocation – JAI CV-M2 User Manual

Page 7: Time slots in camera link

CV-M2

- 6 -

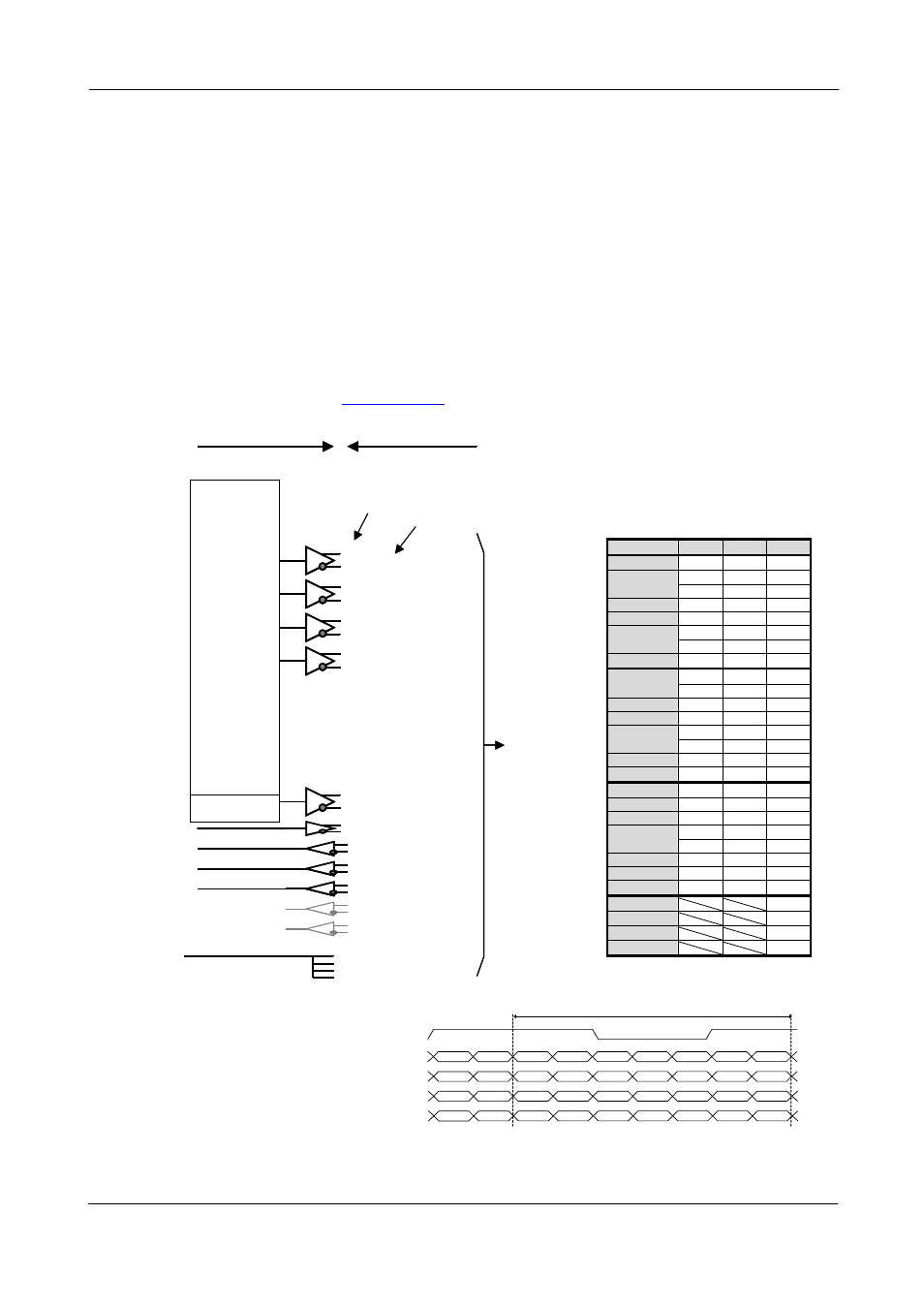

5.4.5. Camera Link interface

The video output is Camera Link, where the 2 channels with 10 or 8 bit video are placed in a

base configuration. The digital output signals follow the Camera Link standardized multiplexed

signal output interface. The output driver is NS type DS90CR285, and the receiver is NS type

DS90CR286.

The data bits from the digital video, FVAL, LVAL, DVAL and EEN are multiplexed into the twisted

pairs, which are a part of the Camera Link. Trigger signals and the serial camera control are

feed directly through its own pairs. The trigger input can also be TTL on the 12 pin connector.

(TI=0 for CL. TI=1 for 12 pin). The serial camera control can be switches between the 12 pin

connector or CL by an internal switch HR/CL. Refer to 7.2

The 26 pin MDR connector pin assignment follows the Camera Link base configuration.

For a detailed description of Camera Link specifications, please refer to the Camera Link

standard specifications found on

1

14

13

26

X0

X1

X2

X3

Xclk

SerTFG

SerTC

CC1

CC2

CC3

CC4

Sheilds

4 x

7-1

MUX

8bit 10bit

L2 L0

L3 L1

L4 L2

L5 L3

L6 L4

L7 L5

L8 L6

L9 L7

R2 L8

R3 L9

R4 NC

R5 NC

R6 R8

R7 R9

R8 NC

R9 NC

NC R0

NC R1

NC R2

NC R3

NC R4

NC R5

NC R6

NC R5

LVAL

FVAL

DVAL

EEN

Pclk

A 0 Tx0

A 1 Tx1

A 2 Tx2

A 3 Tx3

A 4 Tx4

A 5 Tx6

A 6 Tx27

A 7 Tx5

B 0 Tx7

B 1 Tx8

B 2 Tx9

B 3 Tx12

B 4 Tx13

B 5 Tx14

B 6 Tx10

B 7 Tx11

C 0 Tx15

C 1 Tx18

C 2 Tx19

C 3 Tx20

C 4 Tx21

C 5 Tx22

C 6 TX16

C 7 Tx17

Tx24

Tx25

Tx26

Tx23

Txclk

15

2

16

3

17

4

19

6

18

5

21

8

7

20

22

9

10

23

24

11

12

25

Pair 1

Pair 2

Pair 3

Pair 5

Pair 4

Pair 7

Pair 6

Pair 8

Pair 9

Pair 10

Pair 11

Sheilds

TXD out

RXD in

Ext. trig 1 in

Ground

Signal

Connector pin

CV-M2 Camera

Camera Link Cable

Camera Signals

To

Frame

Grabber

Ext. Trig 2 in

Camera Link

Pin

1

14

13

26

X0

X1

X2

X3

Xclk

SerTFG

SerTC

CC1

CC2

CC3

CC4

Sheilds

4 x

7-1

MUX

8bit 10bit

L2 L0

L3 L1

L4 L2

L5 L3

L6 L4

L7 L5

L8 L6

L9 L7

R2 L8

R3 L9

R4 NC

R5 NC

R6 R8

R7 R9

R8 NC

R9 NC

NC R0

NC R1

NC R2

NC R3

NC R4

NC R5

NC R6

NC R5

LVAL

FVAL

DVAL

EEN

Pclk

A 0 Tx0

A 1 Tx1

A 2 Tx2

A 3 Tx3

A 4 Tx4

A 5 Tx6

A 6 Tx27

A 7 Tx5

B 0 Tx7

B 1 Tx8

B 2 Tx9

B 3 Tx12

B 4 Tx13

B 5 Tx14

B 6 Tx10

B 7 Tx11

C 0 Tx15

C 1 Tx18

C 2 Tx19

C 3 Tx20

C 4 Tx21

C 5 Tx22

C 6 TX16

C 7 Tx17

Tx24

Tx25

Tx26

Tx23

Txclk

15

2

16

3

17

4

19

6

18

5

21

8

7

20

22

9

10

23

24

11

12

25

Pair 1

Pair 2

Pair 3

Pair 5

Pair 4

Pair 7

Pair 6

Pair 8

Pair 9

Pair 10

Pair 11

Sheilds

TXD out

RXD in

Ext. trig 1 in

Ground

Signal

Connector pin

CV-M2 Camera

Camera Link Cable

Camera Signals

To

Frame

Grabber

Ext. Trig 2 in

Camera Link

Pin

Port/Signal 8bit

10bit Pin No.

Port A0

L2 L0 Tx0

Port A1

L3 L1 Tx1

Port A2

L4 L2 Tx2

Port A3

L5 L3 Tx3

Port A4

L6 L4 Tx4

Port A5

L7 L5 Tx6

Port A6

L8 L6 Tx27

Port A7

L9 L7 Tx5

Port B0

R2 L8 Tx7

Port B1

R3 L9 Tx8

Port B2

R4 NC Tx9

Port B3

R5 NC Tx12

Port B4

R6 R8 Tx13

Port B5

R7 R9 Tx14

Port B6

R8 NC Tx10

Port B7

R9 NC Tx11

Port C0

NC R0 Tx15

Port C1

NC R1 Tx18

Port C2

NC R2 Tx19

Port C3

NC R3 Tx20

Port C4

NC R4 Tx21

Port C5

NC R5 Tx22

Port C6

NC R6 Tx16

Port C7

NC R7 Tx17

LVAL

Tx24

FVAL

Tx25

DVAL

Tx26

EEN

Tx23

Camera Link bit allocation

TxCLK

A7

A6

EEN

C7

B7

B6

A7

A6

C6

C3

C2

DVAL

FVAL

C5

C4

C3

C2

LVAL

B2

B1

C1

C0

B4

B3

B2

B1

B5

A1

A0

B0

A5

A3

A2

A1

A0

A4

TxOUT3

TxOUT2

TxOUT1

TxOUT0

1 pi xel cycl e

Time slots in Camera Link

Fig. 7. Principle diagram for Camera Link base configuration interface