Advanced chipset features – Intel MB820 User Manual

Page 40

BIOS SETUP

36

MB820 User’s Manual

Advanced Chipset Features

This Setup menu controls the configuration of the chipset.

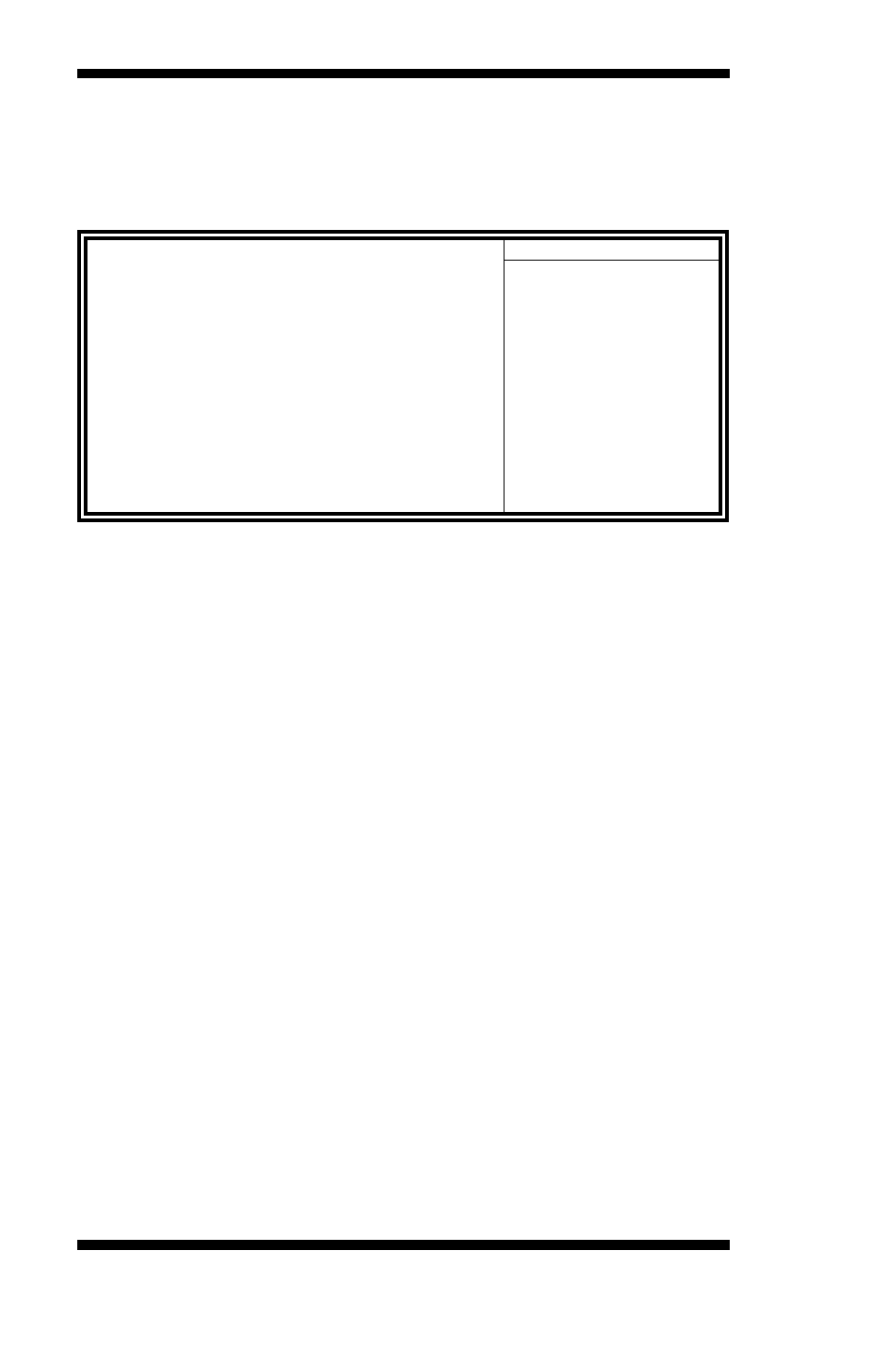

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

DRAM Timing Selectable

By SPD

ITEM HELP

CAS Latency Time

2.5

Menu Level

Active to Precharge Delay

7

DRAM RAS# to CAS# Delay

3

DRAM RAS# Precharge

3

Memory Frequency For

Auto

System BIOS Cacheable

Enabled

Video BIOS Cacheable

Enabled

Memory Hole at 15M-16M

Disabled

Delay Prior to Thermal

16 Min

AGP Aperture Size (MB)

128

Init Display First

PCI Slot

DRAM Data Integrity Mode

Non-ECC

DRAM Timing Selectable

This option refers to the method by which the DRAM timing is selected.

The default is By SPD.

CAS Latency Time

You can configure CAS latency time in HCLKs as 2 or 2.5 or 3. The

system board designer should set the values in this field, depending on the

DRAM installed. Do not change the values in this field unless you change

specifications of the installed DRAM or the installed CPU.

Active to Precharge Delay

The default setting for the Active to Precharge Delay is 7.

DRAM RAS# to CAS# Delay

This option allows you to insert a delay between the RAS (Row Address

Strobe) and CAS (Column Address Strobe) signals. This delay occurs

when the SDRAM is written to, read from or refreshed. Reducing the

delay improves the performance of the SDRAM.

DRAM RAS# Precharge

This option sets the number of cycles required for the RAS to accumulate

its charge before the SDRAM refreshes. The default setting for the Active

to Precharge Delay is 3.