1 processor and cache, 1 l1 and l2 cache, 2 power3-ii architecture – IBM 610 User Manual

Page 18: 1 l1 and l2 cache 2.1.2 power3-ii architecture

10

pSeries 610 Models 6C1 and 6E1 Technical Overview and Introduction

2.1 Processor and cache

The IBM®

^

™ pSeries™ 610 Models 6C1 and 6E1 have two processor card slots

and can accommodate two different processor cards, a 1-way 375 MHz or a 1-way 450 MHz.

Note that slot 1 must have a processor card installed for normal operation.

If your system unit uses two processor cards, both processor cards must be of the same clock

speed.

2.1.1 L1 and L2 cache

Models 6C1 and 6E1 use a 64 KB data and a 32 KB instruction 128-way set associative L1

cache. The size of both data and instruction cache reduces the number of cache misses,

results in more cache hits, and maximizes performance. Both data and instruction cache are

parity protected.

The L1 cache is effectively supplemented by a 4 MB 4-way set associative L2 cache, which is

located on the 375 MHz processor card (8 MB for the 450 MHz processor card). The speed of

the L2 cache is dependent upon the processor speed. The POWER3-II uses a private 32-byte

L2 cache bus, operated at 250 MHz with the 375 MHz processor card (2:3 ratio) and operated

at 225 MHz with the 450 MHz processor card (1:2 ratio). Both the enhanced clock speed and

4-way set associative L2 cache improve cache efficiency. The L2 controller uses a least

recently used (LRU) algorithm to avoid replacing recently used cache data and a set

prediction mechanism that helps reduce L2 cache misses.

The L2 cache uses a direct mapped cache methodology. There is a dedicated external

interface to the L2 cache not shared with the 6XX bus. This allows concurrent access to both

the L2 cache and the 6XX bus.

2.1.2 POWER3-II architecture

The POWER3-II processor offers technical leadership for floating point applications and

high-performance numeric intensive computing (NIC) workstations by integrating two

floating-point, three fixed-point, and two load/store execution units in a single 64-bit POWER3

implementation.

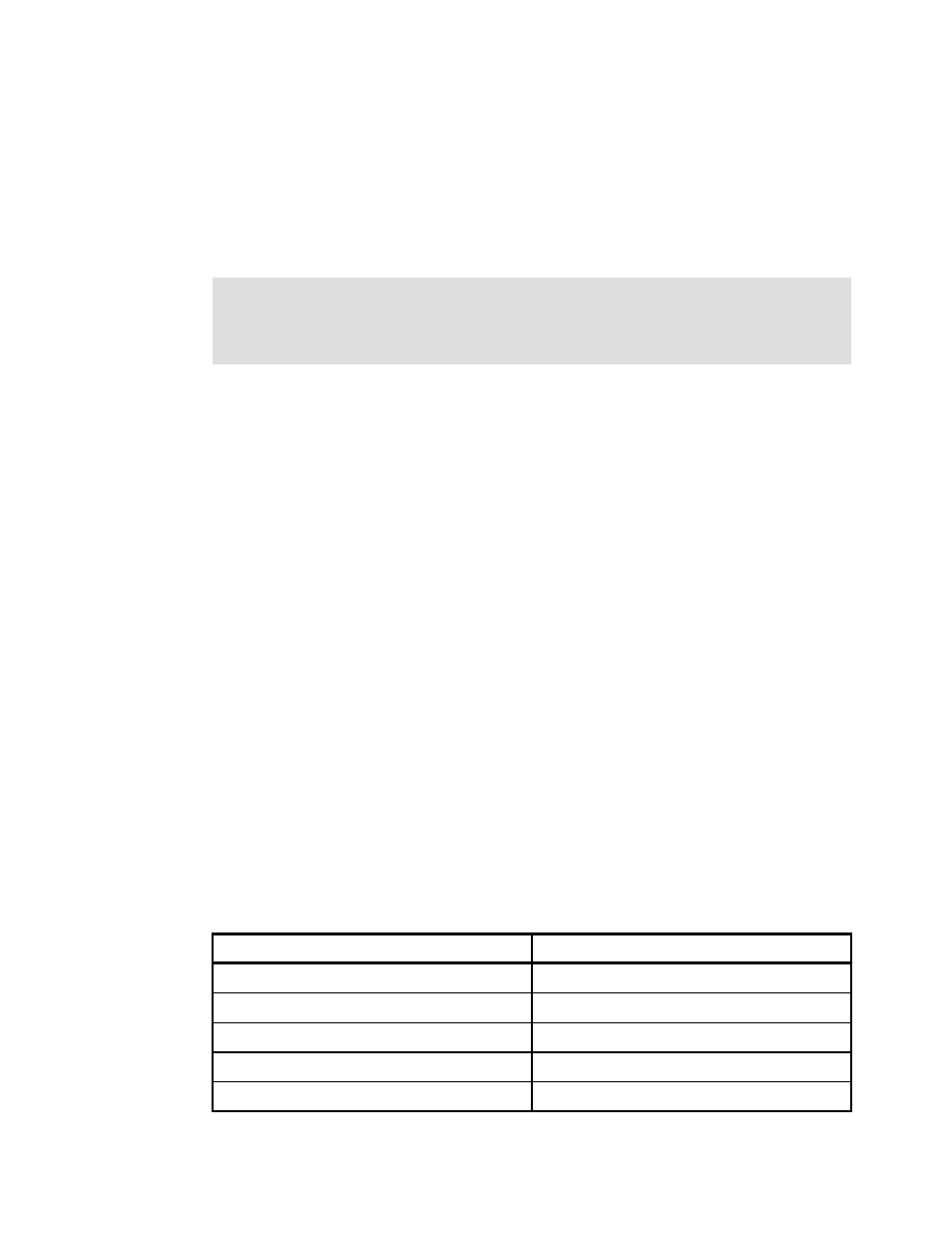

Table 2-1 lists some of the technical features of the POWER3-II processors.

Table 2-1 Technical features of POWER3-II

Note: Installing a processor card into your system unit may require updating the firmware.

A diskette or CD-ROM is included with your new processor card if that is required. Check

also the following Web page for the latest available firmware:

Description

POWER3-II

Chip Die Size

163 mm

2

Transistors

23 million

Power Avg/Max

26W/33W@375 MHz, 31W/42W@450 MHz

CMOS Technology

7S, 6 layers metal, copper interconnect

Lithography

0.22 µm