The dsp’s global bus address lines, The dsp’s global bus data lines – Sundance SMT300Q v.1.6 User Manual

Page 38

User Manual (QCF42); Version 3.0, 8/11/00; © Sundance Multiprocessor Technology Ltd. 1999

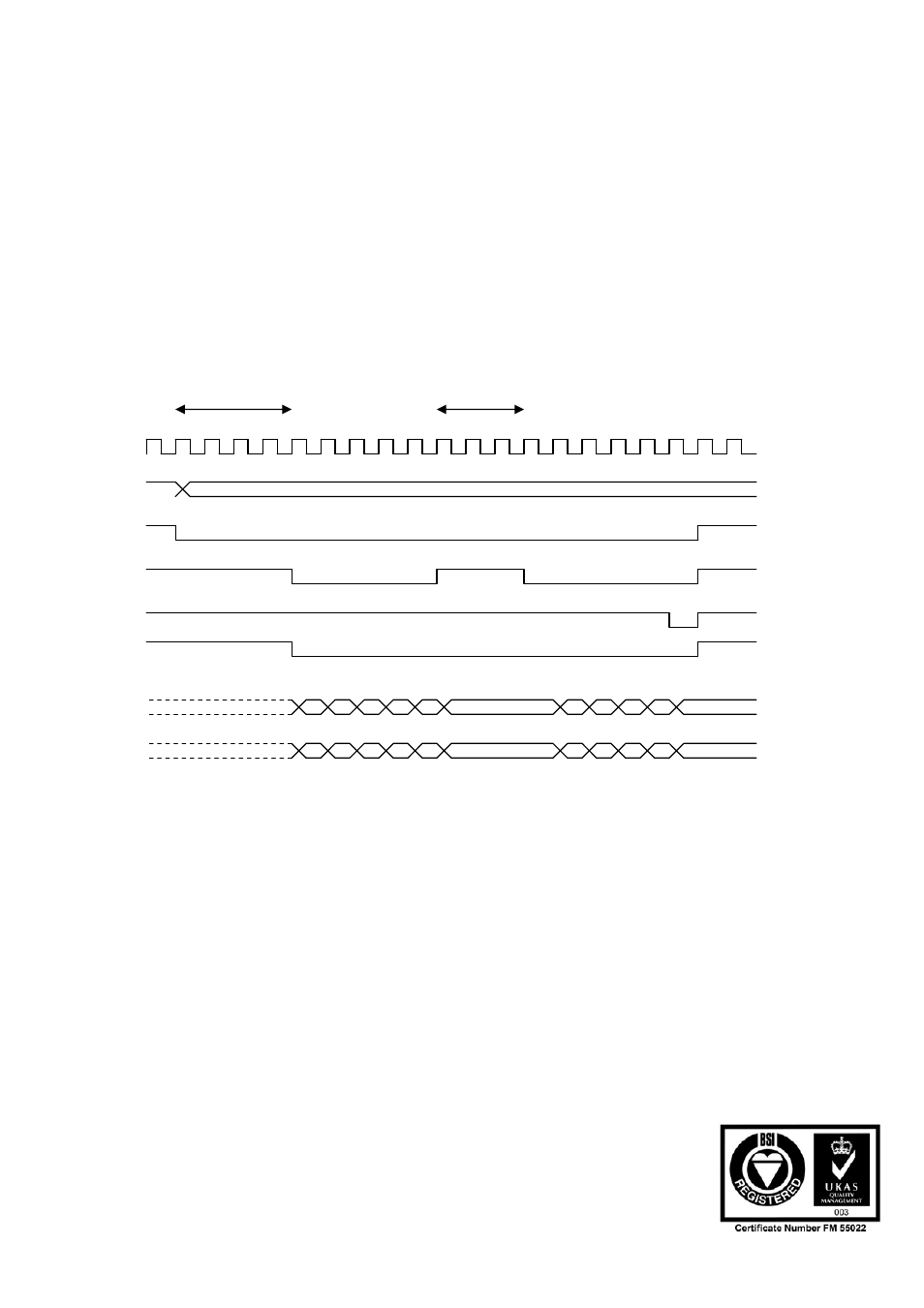

LCLK

STRB1

RDY1

STAT0

AE/DE

A[30..0]

D[31..0]

A0..A30

The DSP’s global Bus address lines

D0..D31

The DSP’s global Bus data lines

IIOF0, IIOF1 & IIOF2

The DSP’s Interrupt signals. These are open collector signals on the SMT300Q.

They can be driven by the DSP to generate an interrupt to the host, or they can be

driven by the host to interrupt the DSP.

In the timing diagram below all signals change relative to the rising LCLK signal. This

signal is the H1 clock signal of the DSP when using the DSP global bus in

synchronous mode (see SMT335 User Guide).

Figure 9 : Timing diagram for DSP local bus access

* LCLK Period =30nS, frequency is 33MHz.

The DSP initiates a global bus R/W by asserting the STRB1 low and STAT[1:3}

change (see TIM Spec for details of STAT[1..3]). Once the arbitration unit detects

this, it waits for the last cycle of the Local bus to be completed by the CompactPCI

Bridge, before allowing the DSP to become Bus Master. Once the DSP is Master the

arbitration unit drives AE and DE low to enable the DSP’s address and data lines.

RDY1 is driven low by the arbitor to indicate to the DSP, on the next rising LCLK, that

the data packet has been transferred. If the input FIFO (256 Words Deep) becomes

full, the arbitration logic de-asserts the RDY1 signal to indicate a hold-off state. Once

the data has been transferred from the FIFO to the CompactPCI bus RDY1 is re-

asserted to continue the transfer. The end of the burst access is indicated by

asserting STAT0 low. If RDY1 is not active then STAT0 should remain asserted until

ready is asserted and the final data transaction has been completed.

It is possible for a deadlock condition to arise, i.e. the CompactPCI bus is trying to

read from the SMT300Q resources while the DSP is reading from the CompactPCI

STAT[1.3]

TIMReq FIFO

Full