8 comport to compactpci interface – Sundance SMT300Q v.1.6 User Manual

Page 23

User Manual (QCF42); Version 3.0, 8/11/00; © Sundance Multiprocessor Technology Ltd. 1999

8 ComPort to CompactPCI Interface

The ComPort interface is memory mapped to the CompactPCI Bridge as illustrated in

table 1 : I/O address space map. The ComPort uses the Control and Data registers to

detect the state of the input and output FIFOs. The following section describes the bit

definitions for these registers.

8.1 ComPort Registers (Offset 0x10, BAR1)

The host is connected to the first TIM site using Comport 3 (T1C3). This port is bi-

directional and will automatically switch direction to meet a request from either the

host or the DSP. Both input and output registers are 32 bits wide. Data can only be

written to COMPORT_OUT when STATUS[OBF] is 0. Data received from the DSP is

stored in COMPORT_IN and STATUS[IBF] is set to 1. Reading COMPORT_IN will

clear STATUS[IBF] and allow another word to be received from the DSP.

8.2 Control

Register (Offset 0x14, BAR1)

The CONTROL register can only be written. It contains flags, which control the boot

modes of the first TIM site.

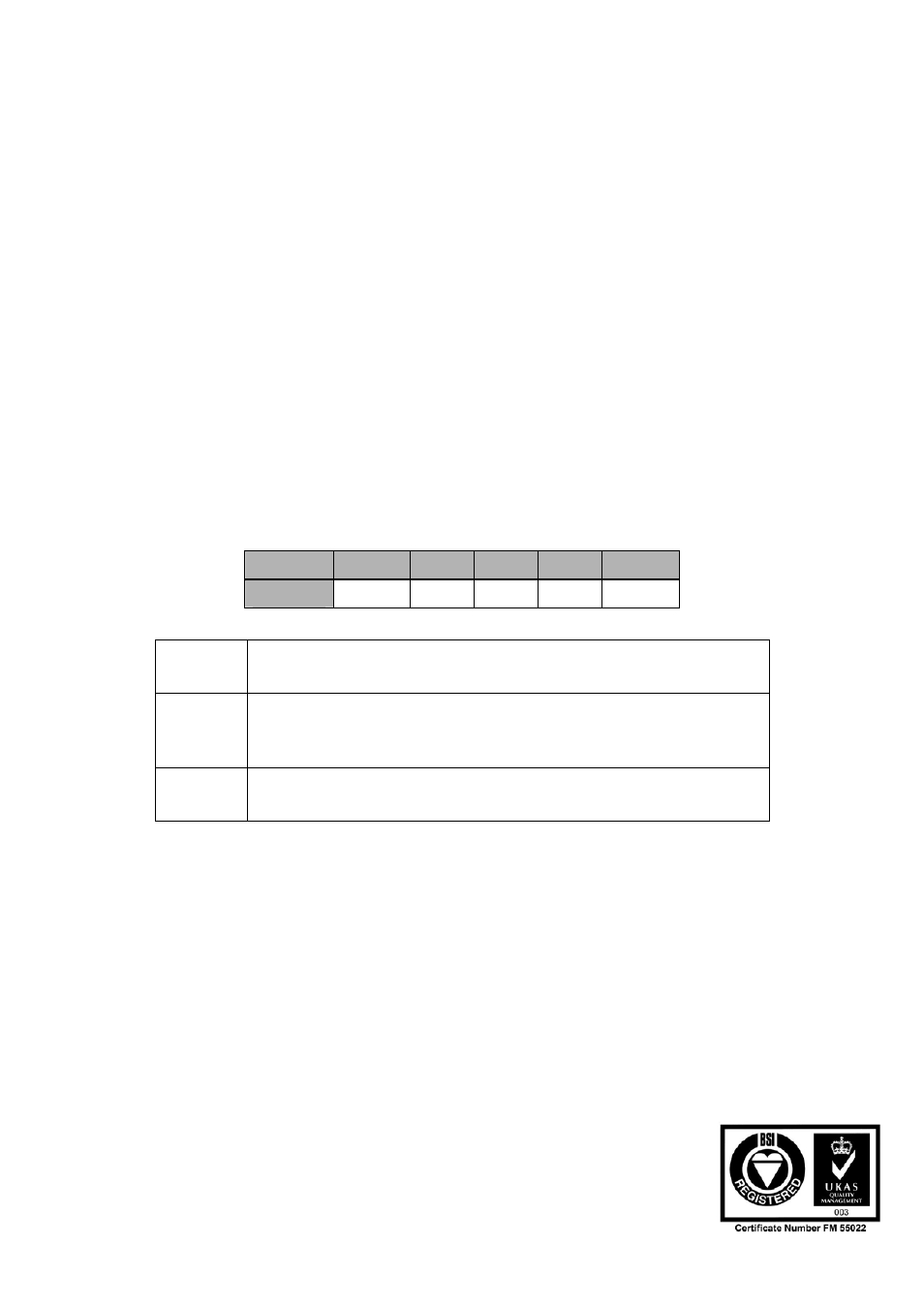

Table 15 : Control Register

Note. On CompactPCI system reset, RESET is asserted to the TIM site.

7-5

4

3

2

1

0

notNMI IIOF2 IIOF1 IIOF0 RESET

RESET

Write a 1 to this bit to assert the reset signal to the TIM

module on the SMT300Q.

IIOF0

IIOF1

IIOF2

These bits connect to the corresponding pins on the TIM site

1. Writing 0 causes the corresponding IIOF line to go low.

NotNMI

A 0 written to this bit will assert the active low NMI to the

TIM.