Pch lan controller enable or disable onboard nic – IBASE FWA8308 User Manual

Page 28

27

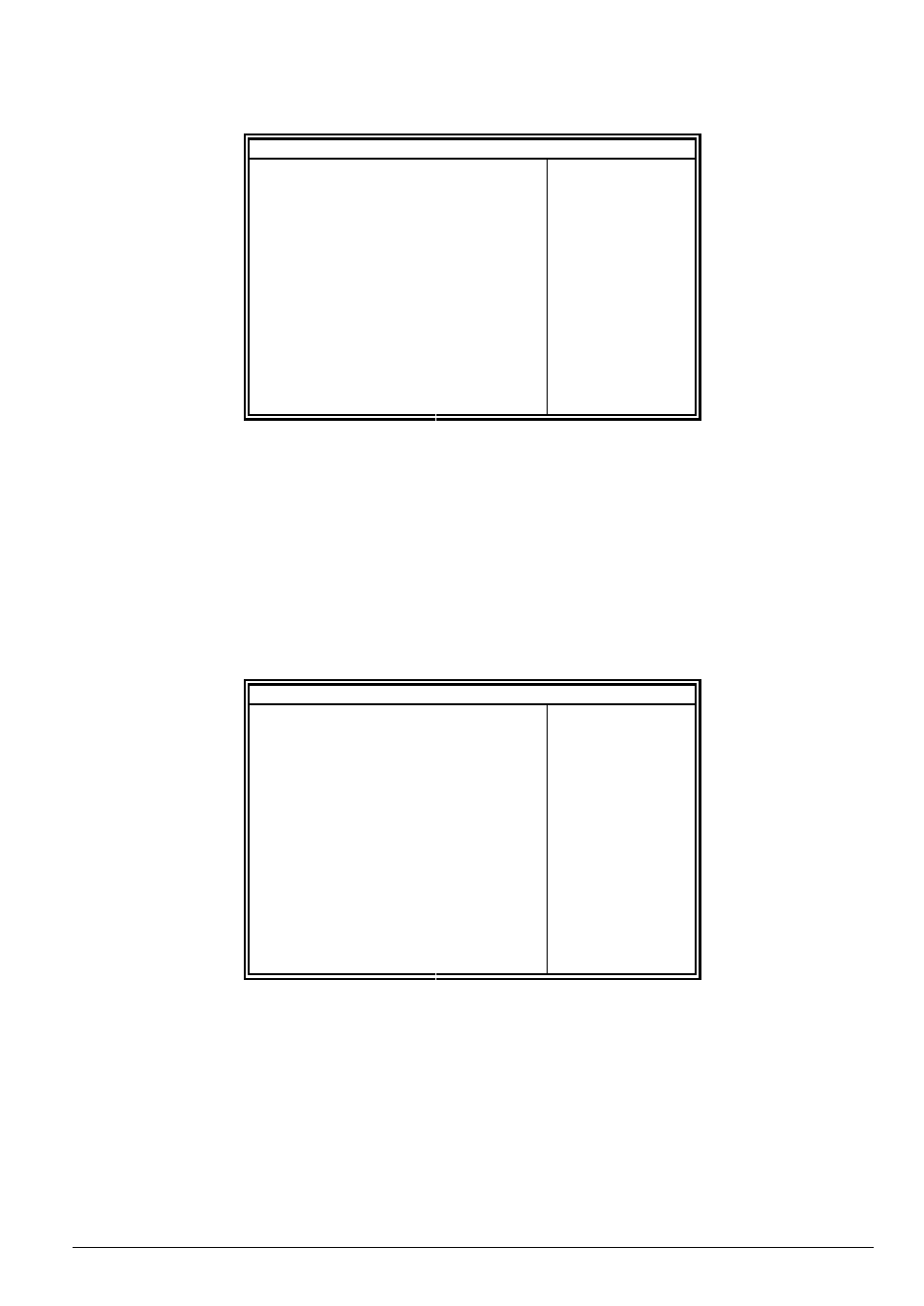

PCH-IO Configuration

This section allows you to configure the North Bridge Chipset.

Aptio Setup Utility

Main Advanced

Chipset

Boot

Security

Save & Exit

Intel PCH RC Version 1.6.2.0

→ ←

Select Screen

↑↓

Select Item

Enter: Select

+- Change Field

F1: General Help

F2: Previous Values

F3: Optimized Default

F4: Save ESC: Exit

Intel PCH SKU Name

C226

Intel PCH Rev ID

O5/C2

► PCI Express Configuration

► USB Configuration

► PCH Azalia Configuration

► BIOS Security Configuration

PCH LAN Controller

[Enabled]

Wake on LAN

DeepSx Power Policies

Display Logic

CLKRUN# Logic

SB CRID

[Enabled]

[Disabled]

[Enabled]

[Enabled]

[Disabled]

SLP_S4 Assertion Width

[4-5 Seconds]

Restore AC Power Loss

[Last State]

PCH LAN Controller

Enable or disable onboard NIC.

Wake on LAN

Enable or disable integrated LAN to wake the system. (The Wake On LAN cannot be disabled if ME is on at Sx

state.)

SLP_S4 Assertion Width

Select a minimum assertion width of the SLP_S4# signal.

Restore AC Power Loss

Select AC power state when power is re-applied after a power failure.

PCI Express Configuration

Main Advanced

Chipset

Boot

Security

Save & Exit

PCI Express Configuration

→ ←

Select Screen

↑↓

Select Item

Enter: Select

+- Change Field

F1: General Help

F2: Previous Values

F3: Optimized Default

F4: Save ESC: Exit

PCI Express Clock Gating

[Enabled]

DMI Link ASPM Control

[Enabled]

DMI Link Extended Synch Control

[Disabled]

PCIE Root Port Function

[Disabled]

Subtractive Decode

[Disabled]

PCIE Port 1 is assign

► PCI Express Root Port 2

► PCI Express Root Port 3

► PCI Express Root Port 4

► PCI Express Root Port 5

► PCI Express Root Port 6

► PCI Express Root Port 7

► PCI Express Root Port 8

PCI Express Clock Gating

Enable or disable PCI Express Clock Gating for each root port.

DMI Link ASPM Control

The control of Active State Power Management on both NB side and SB side of the DMI link.

PCIE Root Port Function

Enable or disable PCI express Root Port function swapping.