2 – i2c master controller register description, I2c master controller register description, Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 85

DS4830 User’s Guide

85

10.2

– I2C Master Controller Register Description

Following are the registers that are used to control the I

2

C Master Interface, which is the MSDA and MSCL pins. These

registers are used to control the I

2

C master interface if it is operating as either a master or slave. The bit descriptions

below detail how to use these registers when operating in master mode. When operating in slave mode, some of the bits

and registers have different functionality. See the I

2

C Slave Interface for more information on how to control the I

2

C

Master Interface when it is operating as a slave.

10.2.1

– I

2

C Master Control Register (I2CCN_M)

Address: M1[0Ch]

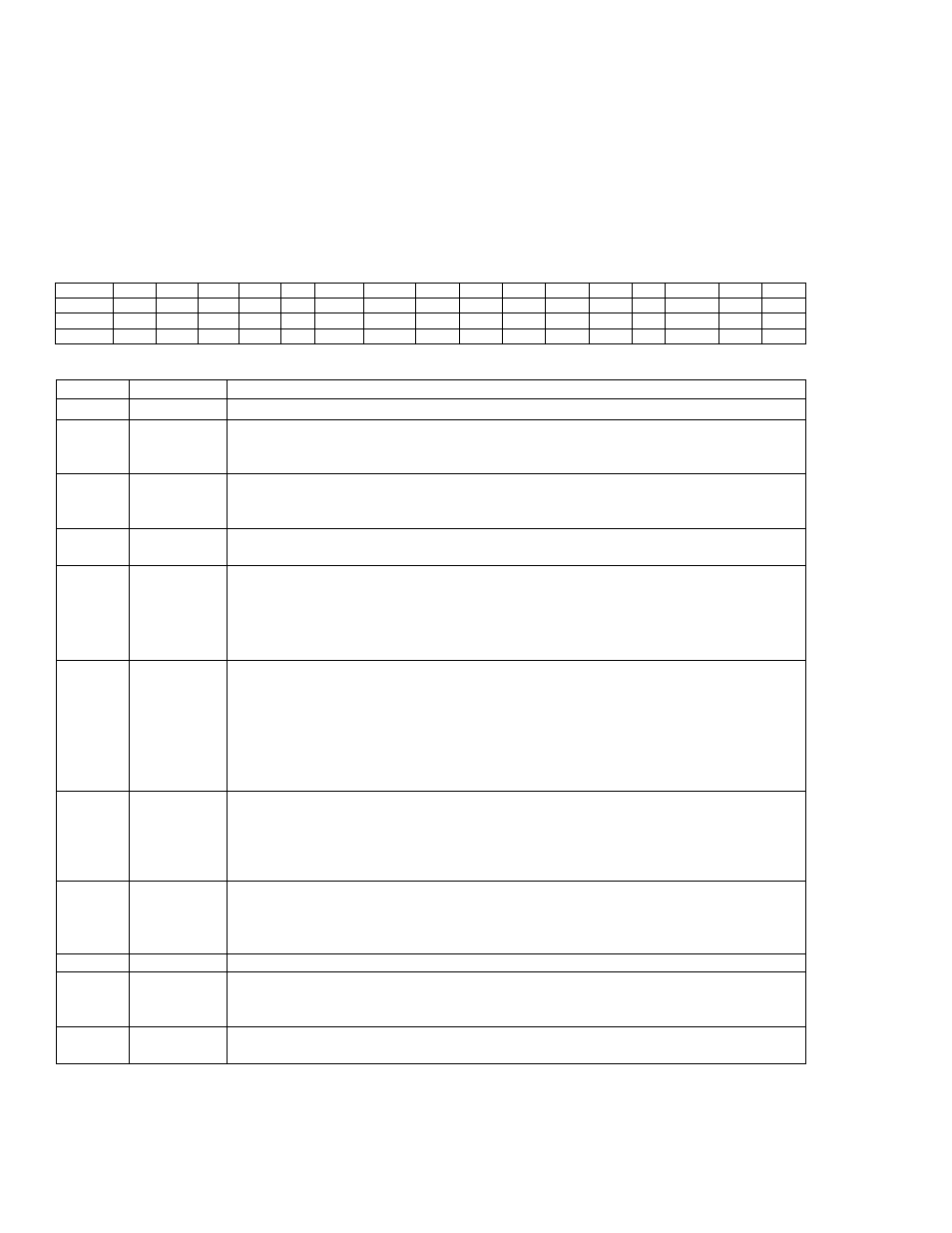

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

SMB_MOD I2CSTREN I2CGCEN I2CSTOP

I2CSTART

I2CACK I2CSTRS

-

-

I2CMST

I2CEN

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

Access

r

r

r

r

r

r

rw

rw

rw

rw

rw

rw

r

r

rw*

rw*

* Unrestricted Read. Unrestricted write access when I2CBUSY=0. Writes to I2CEN are disabled when I2CBUSY=1.

BIT

NAME

DESCRIPTION

15:11

Reserved

Reserved. The user should write 0 to these bits.

10

SMB_MOD

SMBus Mode Enable. This bit enables the SMBUS timeout feature only when

the master I

2

C interface (MSDA and MSCL) is enabled to be a slave interface.

See the Operation as a Slave section for more details.

9

I2CSTREN

I

2

C Master Clock Stretch Enable.

Setting this bit to ‘1’ will stretch the clock (hold

SCL low) at the end of the clock cycle specified by I2CSTRS. Clearing this bit

disables clock stretching.

8

I2CGCEN

I

2

C General Call Enable. This bit has no function when operating in master

mode.

7

I2CSTOP

I

2

C

STOP Enable. Setting this bit to

‘1’ generates a STOP condition. This bit is

automatically cleared to

‘0’ after the STOP condition has been generated.

The setting of I2CSTOP will start the timeout timer if enabled. If the timeout timer

expires before the STOP condition is generated, the I2CTOI flag is set, which can

generate an interrupt if enabled. A timeout will also clear the I2CSTOP bit.

6

I2CSTART

I

2

C

START Enable. Setting this bit to

‘1’ generates a START or repeated

START condition. This bit is automatically cleared to

‘0’ after the START

condition has been generated.

The setting of I2CSTART will start the timeout timer if enabled. If the timeout

timer expires before the START condition is generated, the I2CTOI flag is set,

which can generate an interrupt if enabled. A timeout will also clear the

I2CSTART bit.

5

I2CACK

I

2

C Master Data Acknowledge Bit. This bit selects the acknowledge bit returned

by the master I

2

C controller while acting as a receiver. Setting this bit to

‘1’ will

generate a NACK (leaving SDA high). Clearing the I2CACK bit to

‘0’ will generate

an ACK (pulling SDA LOW) during the acknowledgement cycle. This bit will retain

its value unless changed by software or hardware.

4

I2CSTRS

I

2

C Master Clock Stretch Select. Setting this bit to

‘1’ will enable clock

stretching after the falling edge of the 8

th

clock cycle. Clearing this bit to

‘0’ will

enable clock stretching after the falling edge of the 9

th

clock cycle. This bit has no

effect when clock stretching is disabled (I2CSTREN=0).

3:2

Reserved

Reserved. The user should write 0 to these bits.

1

I2CMST

I

2

C Master Mode Enable. Setting this bit to

‘1’ will enable I

2

C master functionality

on the MSDA and MSCL pins. Setting this bit to

‘0’ enables I

2

C slave

functionality. See the I

2

C Slave Interface section for more details.

0

I2CEN

I

2

C Enable. This bit enables the I

2

C Master interface. When set to

‘1’, the I

2

C

Master Interface is enabled. When cleared to

‘0’, the I

2

C function is disabled.

Notes: T

he I2CSTART and I2CSTOP are mutually exclusive. If both bits are set at the same time, it is considered an

invalid operation and the I

2

C controller ignores the request and resets both bits to 0. Setting the I2CSTART bit to 1 while

I2CSTOP = 1 is an invalid operation and is ignored, leaving the I2CSTART bit cleared to 0.