Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 38

DS4830 User’s Guide

38

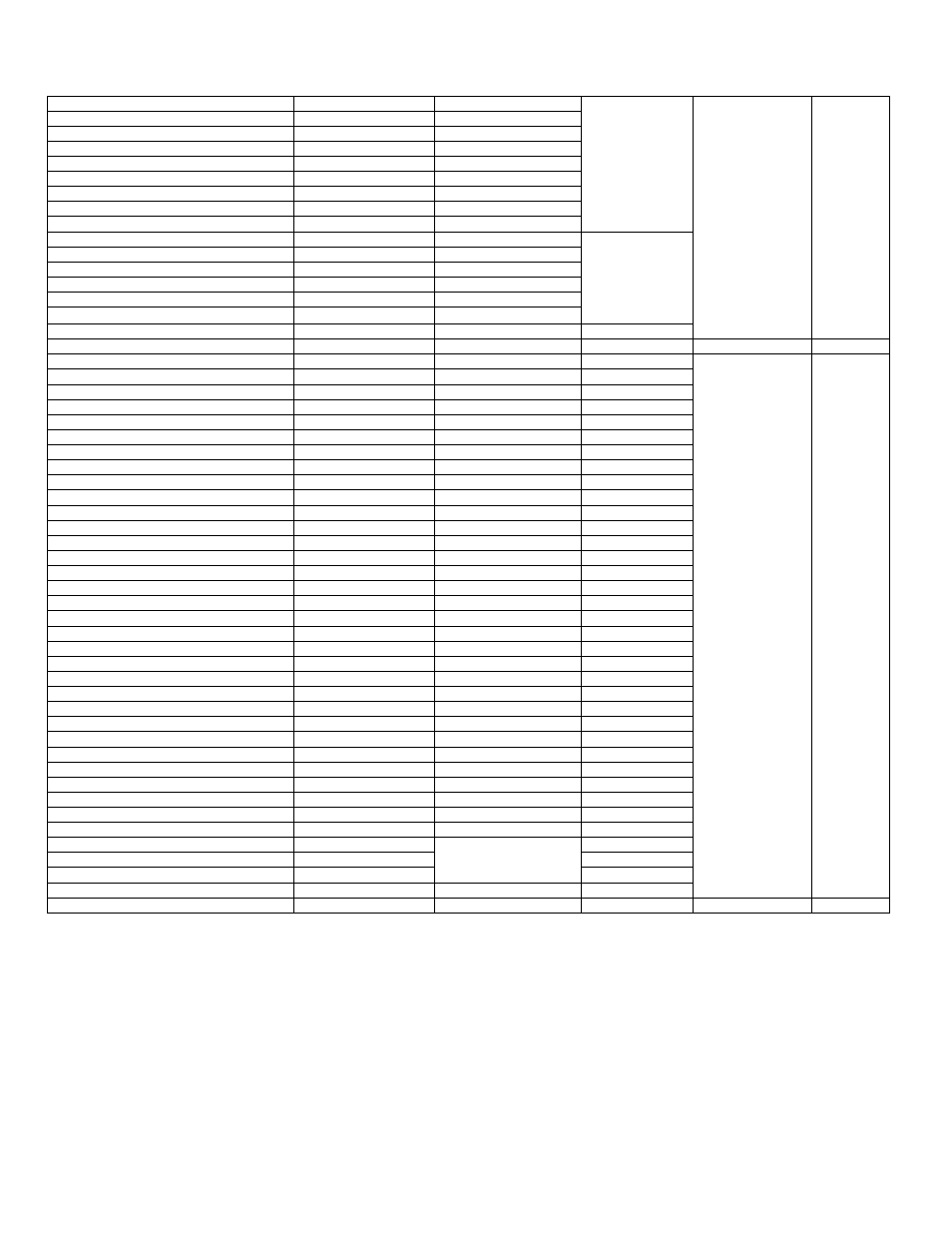

I

2

C Slave Transmit Complete Interrupt

I2CST_S.I2CTXI

I2CIE_S.I2CTXIE

I

2

C Slave Receive Ready Interrupt

I2CST_S. I2CRXI

I2CIE_S.I2CRXIE

I

2

C Slave Clock Stretch Interrupt

I2CST_S.I2CSTRI

I2CIE_S.I2CSTRIE

I

2

C Slave Timeout Interrupt

I2CST_S.I2CTOI

I2CIE_S.I2CTOIE

I

2

C Slave Address Match Interrupt

I2CST_S.I2CAMI

I2CIE_S.I2CAMIE

I

2

C Slave NACK Interrupt

I2CST_S.I2CNACKI

I2CIE_S.I2CNACKIE

I

2

C Slave General Call Interrupt

I2ST_S.I2CGCI

I2CIE_S.I2CGCIE

I

2

C Slave Receiver Overrun Interrupt

I2CST_S.I2CROI

I2CIE_S.I2CROIE

I

2

C Slave Stop Interrupt

I2CST_S.I2CSPI

I2CIE_S.I2CSPIE

ADC Data Available Interrupt

ADST.ADDAI

ADCN.ADDAIE

MIIR2.ADC

Internal Temperature Interrupt

ADST.INTADI

TEMPCN.INT_IEN

External Temperature 0 Interrupt

ADST.EX0ADI

TEMPCN.EX0_IEN

External Temperature 1 Interrupt

ADST.EX1ADI

TEMPCN.EX1_IEN

Sample and Hold 0 Interrupt

ADST.ADDAI

SHCN.SHDAI0_EN

Sample and Hold 1 Interrupt

ADST.ADDAI

SHCN.SHDAI1_EN

3 Wire Interrupt

TWR.TWI

TWR.TWIE

MIIR2.TW

Timer2 Interrupt

GTCN1.GTIF

GTCN1.GTIE

-

IIR.II3

IMR.IM3

LT 0 Interrupt

LTI.IF0

LTIE.IE0

-

IIR.II5

IMR.IM5

LT 1 Interrupt

LTI.IF1

LTIE.IE1

-

LT 2 Interrupt

LTI.IF2

LTIE.IE2

-

LT 3 Interrupt

LTI.IF3

LTIE.IE3

-

LT 4 Interrupt

LTI.IF4

LTIE.IE4

-

LT 5 Interrupt

LTI.IF5

LTIE.IE5

-

LT 6 Interrupt

LTI.IF6

LTIE.IE6

-

LT 7 Interrupt

LTI.IF7

LTIE.IE7

-

LT 8 Interrupt

LTI.IF8

LTIE.IE8

-

LT 9 Interrupt

LTI.IF9

LTIE.IE9

-

LT 10 Interrupt

LTI.IF10

LTIE.IE10

-

LT 11 Interrupt

LTI.IF11

LTIE.IE11

-

LT 12 Interrupt

LTI.IF12

LTIE.IE12

-

LT 13 Interrupt

LTI.IF13

LTIE.IE13

-

LT 14 Interrupt

LTI.IF14

LTIE.IE14

-

LT 15 Interrupt

LTI.IF15

LTIE.IE15

-

HT 0 Interrupt

HTI.IF0

HTIE.IE0

-

HT 1 Interrupt

HTI.IF1

HTIE.IE1

-

HT 2 Interrupt

HTI.IF2

HTIE.IE2

-

HT 3 Interrupt

HTI.IF3

HTIE.IE3

-

HT 4 Interrupt

HTI.IF4

HTIE.IE4

-

HT 5 Interrupt

HTI.IF5

HTIE.IE5

-

HT 6 Interrupt

HTI.IF6

HTIE.IE6

-

HT 7 Interrupt

HTI.IF7

HTIE.IE7

-

HT 8 Interrupt

HTI.IF8

HTIE.IE8

-

HT 9 Interrupt

HTI.IF9

HTIE.IE9

-

HT 10 Interrupt

HTI.IF10

HTIE.IE10

-

HT 11 Interrupt

HTI.IF11

HTIE.IE11

-

HT 12 Interrupt

HTI.IF12

HTIE.IE12

-

HT 13 Interrupt

HTI.IF13

HTIE.IE13

-

HT 14 Interrupt

HTI.IF14

HTIE.IE14

-

HT 15 Interrupt

HTI.IF15

HTIE.IE15

-

SPI Master Transfer Complete

SPICN_M.SPIC

SPICF_M.ESPII

-

SPI Master Write Collision

SPICN_M.WCOL

-

SPI Master Receive Overrun

SPICN_M.ROVR

-

SPI Master Mode Fault

SPICN_M.MODF

SPICN_M.MODFE

-

Watchdog Interrupt

WDCN.WDIF

WDCN.EWDI

N/A

IIR.IIS

IMR.IMS

When an interrupt condition occurs, its individual flag is set, even if the interrupt source is disabled at the local, module, or

global level. Interrupt flags must be cleared within the user interrupt routine to avoid repeated interrupts from the same

source.

Since all interrupts vector to the address contained in the Interrupt Vector (IV) register, the Interrupt Identification Register

(IIR) may be used by the interrupt service routine to determine the module source of an interrupt. The IIR contains a bit

flag for each peripheral module and one flag associated with all system interrupts; if the bit for a module is set, then an

interrupt is pending that was initiated by that module.

In the DS4830 MIIR registers are defined for module 1 and 2. In these modules the DS4830 provides two ways to

determine which block inside a module (for module 1 and 2 only) caused an interrupt to occur. Module 0 and 1 has

Module Interrupt Identification Registers (MIIR1 and MIIR2) that i

ndicate which of the module’s interrupt sources has a