2 memory-access protocol, Figure 8-3 – IBM POWERPC 750GL User Manual

Page 284

User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Bus Interface Operation

Page 284 of 377

gx_08.fm.(1.2)

March 27, 2006

8.2 Memory-Access Protocol

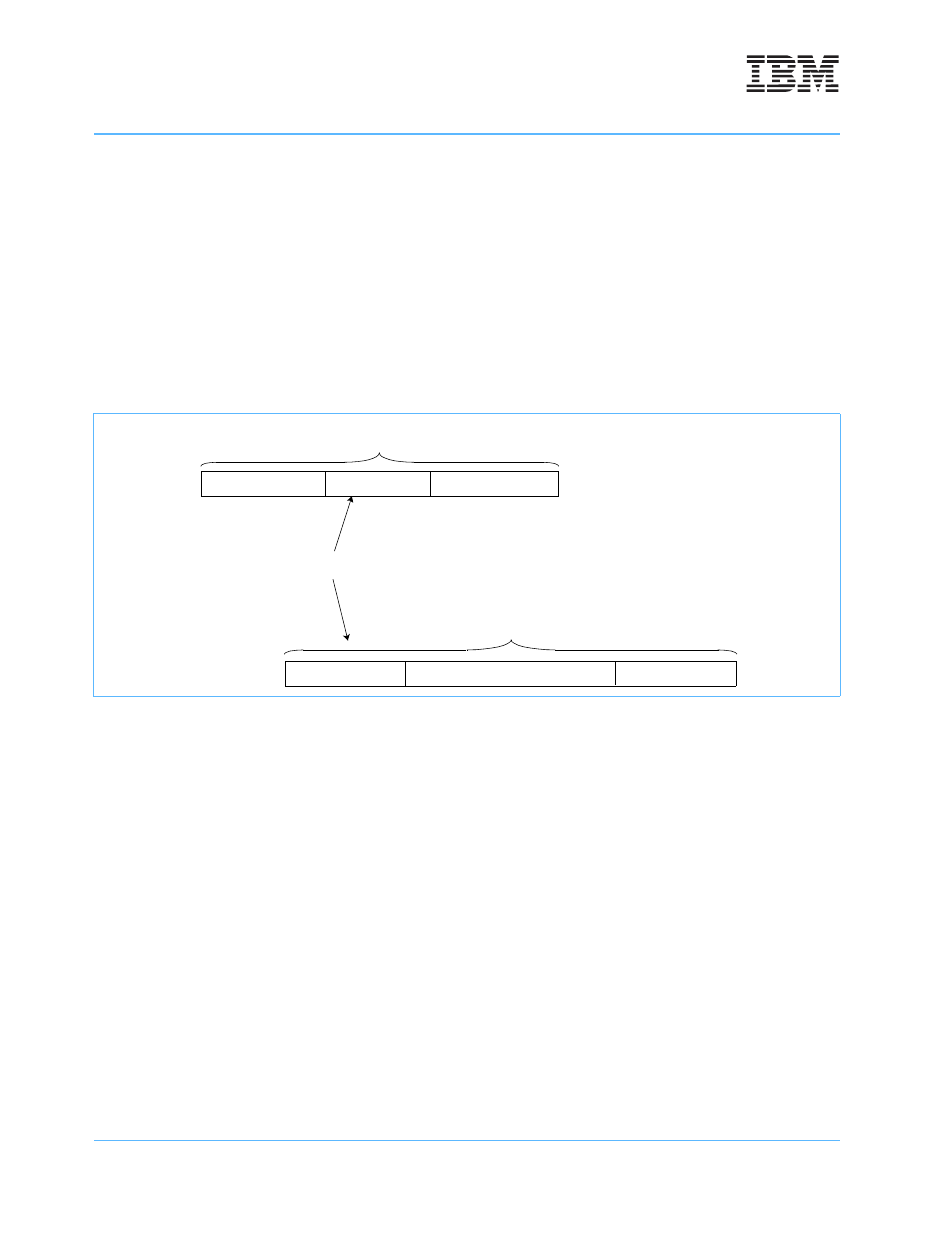

Memory accesses are divided into address and data tenures. Each tenure has three phases—bus arbitration,

transfer, and termination. The 750GX also supports address-only transactions. Note that address and data

tenures can overlap, as shown in Figure 8-3.

Figure 8-3 shows that the address and data tenures are distinct from one another and that both consist of

three phases—arbitration, transfer, and termination. Address and data tenures are independent (indicated in

Figure 8-3 by the fact that the data tenure begins before the address tenure ends), which allows split-bus

transactions to be implemented at the system level in multiprocessor systems. The figure also shows a data

transfer that consists of a single-beat transfer of as many as 64 bits. Four-beat burst transfers of 32-byte

cache lines require data-transfer termination signals for each beat of data.

The basic functions of the address and data tenures are as follows.

Address tenure:

Figure 8-3. Overlapping Tenures on the 750GX Bus for a Single-Beat Transfer

Arbitration

During arbitration, address-bus arbitration signals are used to gain mastership of the

address bus.

Transfer

After the 750GX is the address-bus master, it transfers the address on the address bus. The

address signals and the transfer attribute signals control the address transfer. The address

parity and address-parity error signals ensure the integrity of the address transfer.

Termination

After the address transfer, the system signals that the address tenure is complete or that it

must be repeated.

ARBITRATION

TRANSFER

TERMINATION

ADDRESS TENURE

ARBITRATION

SINGLE-BEAT TRANSFER

TERMINATION

DATA TENURE

INDEPENDENT ADDRESS AND DATA