Rx − 8564 lc – Epson RX-8564LC User Manual

Page 26

RX

−

8564

LC

Page

−

23

ETM12E-01

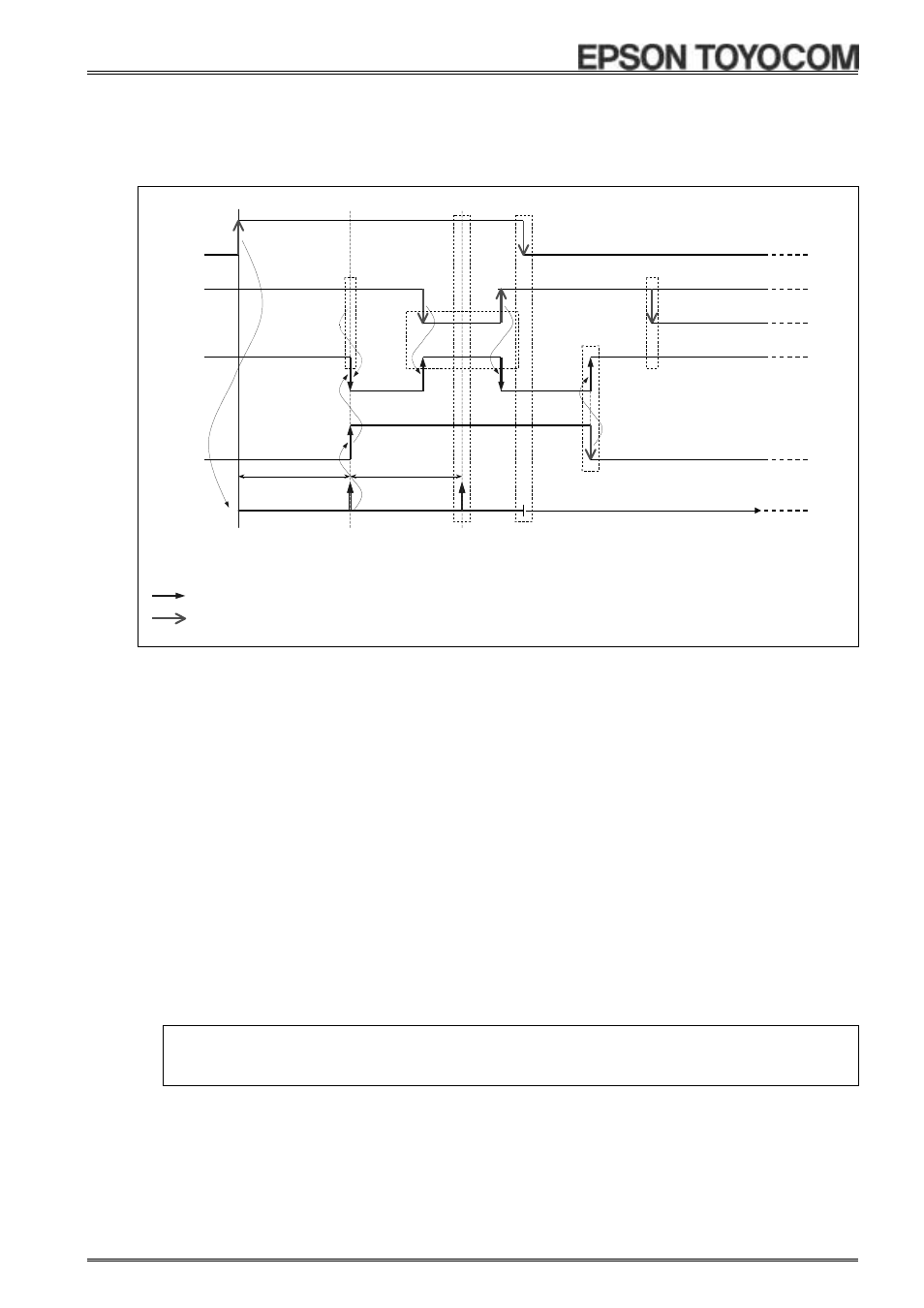

13.2.4. Diagram of fixed-cycle timer interrupt function

13.2.4.1. Operation example of level interrupt mode

(

TI

/

TP

=

"

0

"

)

•

After an interrupt event has occurred, this function operates only once.

TIE bit

/INT output

TF bit

Internal interrupt

processing

TE bit

2nd period

" 1 "

" 0 "

" 1 "

"

0

"

Hi

-

z

"

L

"

"

1

"

" 0 "

∗

Even if the TE bit is cleared to zero, the TF bit value

is held as

"1". Also, the /INT pin is not canceled.

The TF bit value is held until it is directly cleared to

zero.

∗

When the TF bit is cleared to

zero, /INT is canceled.

∗

The fixed-cycle timer function starts (the countdown starts) when the TE bit value changes

from

"0" to "1".

∗

Before starting the fixed-cycle timer interrupt function each time, be sure to write a value

(preset value/Reg-0F[h]) as the timer's down counter value (when TE

=

"0").

RTC's internal operation

Write operation

Start of fixed-cycle timer operation

(1)

(1)

(2)

• • •

01

h

→

00

h

(3)

(6)

(4)

"

1

"

(7)

∗

After the TF bit is cleared to zero, the

/INT pin is set to Hi-Z mode regardless

of the TE bit's value.

• • •

01 h

→

00 h

1st period

(5)

(6)

∗

When TE = "0" the countdown is stopped

∗

Before starting the fixed-cycle timer interrupt function each time, be sure to write a value (preset value/Reg-0F[h])

as the timer's down counter value (when TE

=

"0").

(Note)

Note with caution that the preset value must be set or reset to enable correct operation.

∗

Before entering operation settings, we recommend

first clearing the TE bit to "0"

and then clearing the TF and

TIE

bits to "0" in that order, so that all control-related bits are zero-cleared (=

set to operation stop mode) to prevent

hardware interrupts from occurring inadvertently while entering settings.

(1)

When the TE bit value is changed from "0" to 1", the fixed-cycle timer's countdown begins.

(2) A fixed-cycle timer interrupt event occurs when the down counter value goes from 01h to 00h during a

countdown in which the down counter's count value is decremented at each source clock cycle.

(3) When a fixed-cycle timer interrupt event occurs, the TF bit value is changed to "1".

(4) If the TIE bit = "1" when a fixed-cycle timer interrupt occurs, /TIRQ pin output goes low.

∗

If the TIE bit = "0" when a fixed-cycle timer interrupt occurs, /TIRQ pin output remains Hi-Z.

(5) During the period when the TF bit value is "1" following the occurrence of an interrupt event, the TIE bit can be

set to switch the /INT pin to any status.

(6)

As long as the TE bit value remains “1", the operation sequence "countdown by timer's down counter

→

internal

event processing

→

loading of preset value

→

countdown…" is repeated regardless of the operation mode, etc.

However, this operation sequence has no effect unless the TF bit has been cleared to zero.

∗

If the TE bit value remains "1" and only the TF bit is cleared to zero, (the fixed-cycle timer continues to

operate), note with caution that an interrupt event will occur the next time the counter value changes from

01h to 00h (the TF bit will become "1"

again and the /INT pin status will be

"L").

(6)

When the TF bit = "1" its value is retained until it is cleared to zero.

Even when the TE bit is cleared to zero, the TF bit value is retained as

"1" and the /INT pin status is not reset.

(7)

After the TF bit is cleared to zero, the /TIRQ pin is set to Hi-Z status regardless of the TIE bit's value.