Rx − 8564 lc – Epson RX-8564LC User Manual

Page 16

RX

−

8564

LC

Page

−

13

ETM12E-01

13.1.2. Control register 2

(

Reg

−

01

[h]

)

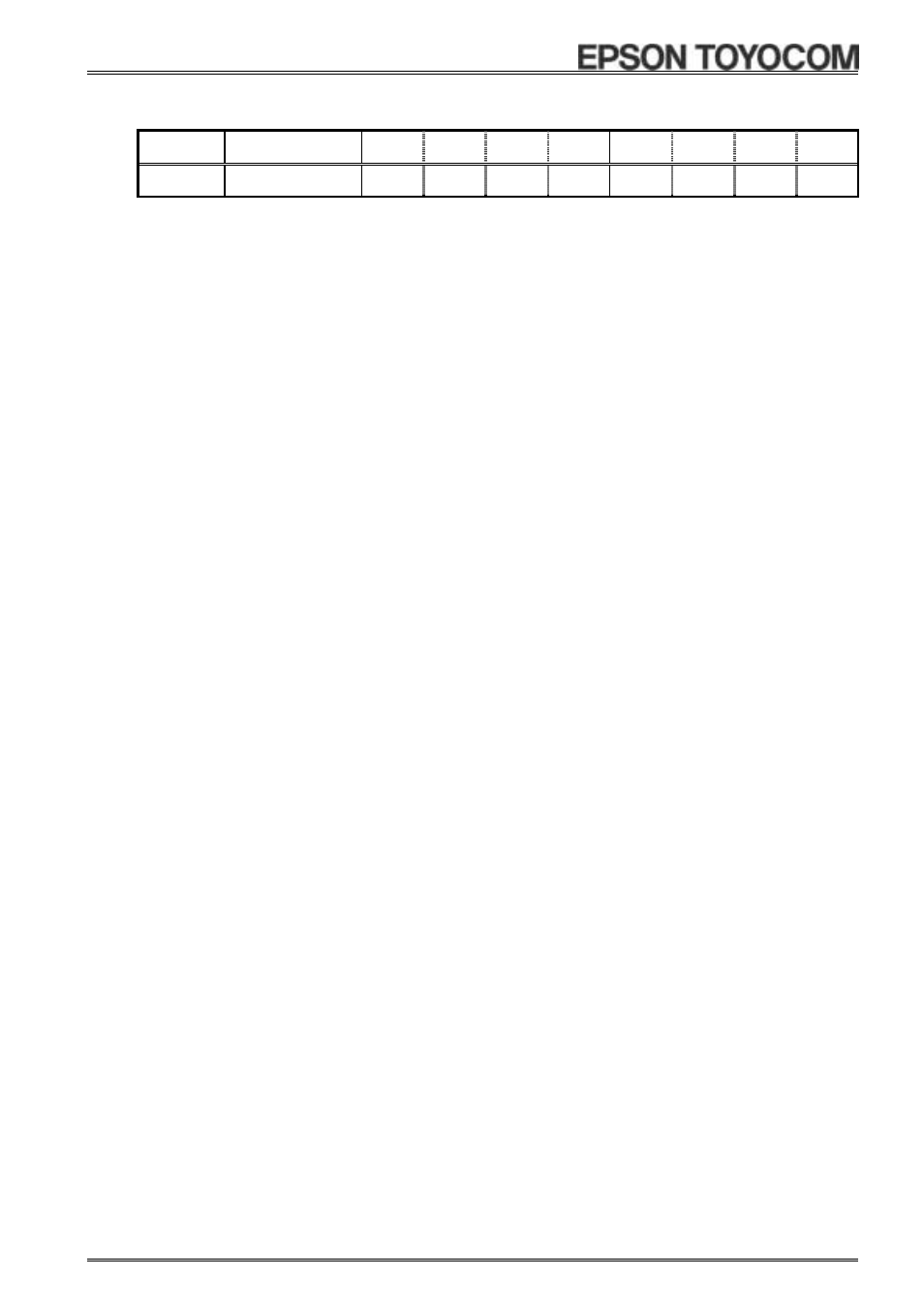

Address [h]

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

01

Control 2

0

×

0

TI

/

TP

AF

TF

AIE

TIE

•

This register is used to monitor various interrupt event settings and the conditions under which various interrupt-

related events occur.

1) TI

/

TP bit

(

Interrupt Signal Output Mode Select. Interrupt / Periodic

)

When a fixed-cycle timer interrupt event occurs (when the TF bit goes from "0"

to 1")

, this bit specifies

whether the interrupt operation occurs just once or repeatedly.

Writing "1"

to this bit sets repeated operation.

Writing "0"

to this bit sets single-shot operation.

∗

For details, see "9.2. Fixed-cycle Timer Interrupt Function ".

2) AF bit

(

Alarm Flag

)

This is a flag bit that retains the result when an alarm interrupt event has been detected.

When an alarm interrupt event occurs, this bit's value changes from "0" to "1".

∗

For details, see "9.3. Alarm Interrupt Function".

3) TF bit

(

Timer Flag

)

This is a flag bit that retains the result when a fixed-cycle timer interrupt event has been detected.

When a fixed-cycle timer interrupt event occurs, this bit's value changes from "0" to "1".

∗

For details, see "9.2. Fixed-cycle Timer Interrupt Function ".

4) AIE bit

(

Alarm Interrupt Enable

)

This bit sets the operation of the /INT interrupt signal when an alarm interrupt event has occurred (the AF bit

value changes from "0"

to

"1").

When a "1"

is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be

output from /INT pin.

Writing "0"

to this bit prohibits low-level output from the /INT pin.

∗

For details, see "9.3. Alarm Interrupt Function".

5) TIE bit

(

Timer Interrupt Enable

)

This bit sets the operation of the /INT interrupt signal when a fixed-cycle interrupt event has occurred (the

TF bit value changes from "0"

to

"1").

When a "1"

is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be

output from /INT pin.

Writing "0"

to this bit prohibits low-level output from the /INT pin.

∗

For details, see "9.2. Fixed-cycle Timer Interrupt Function ".