Rx − 8564 lc – Epson RX-8564LC User Manual

Page 20

RX

−

8564

LC

Page

−

17

ETM12E-01

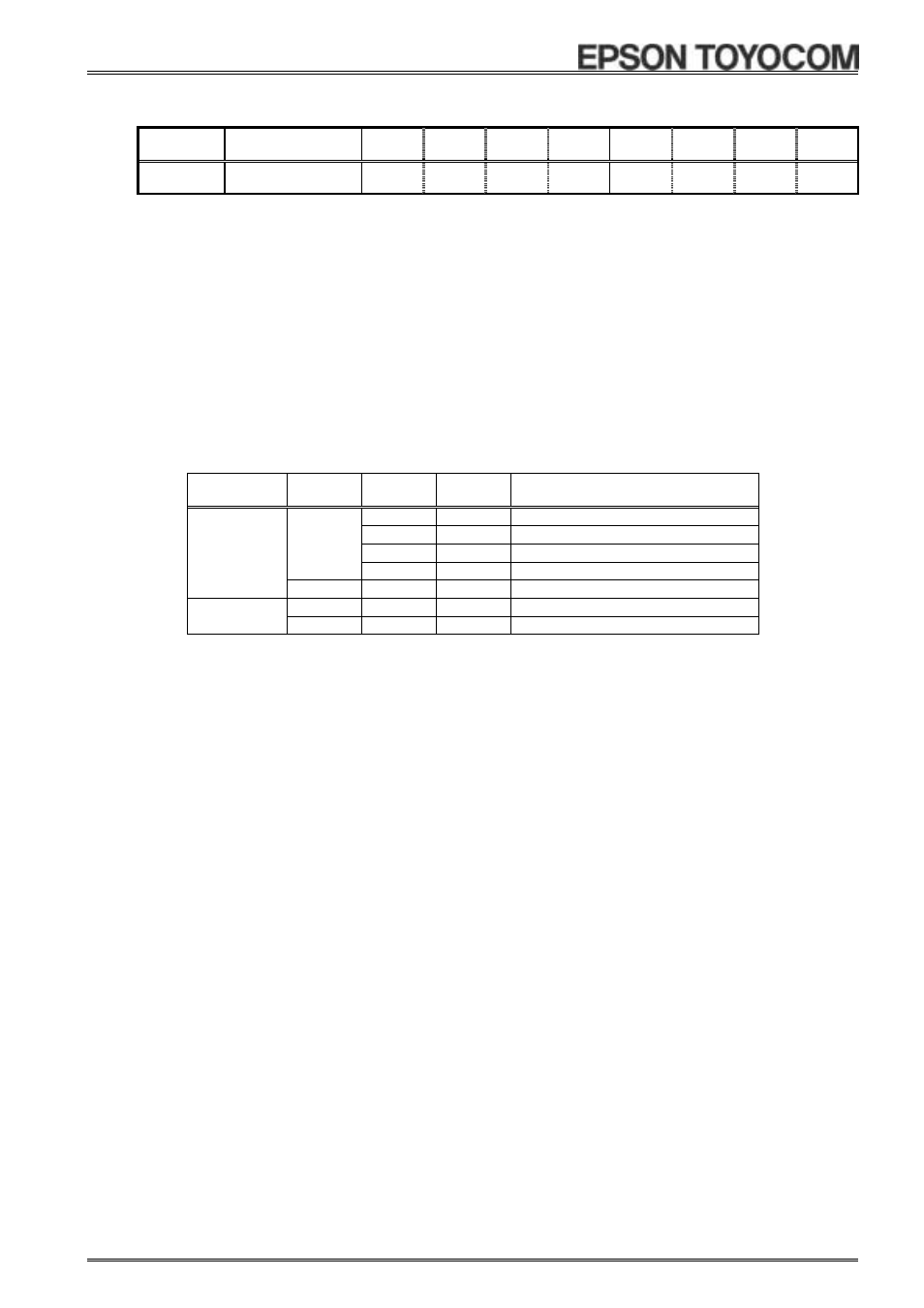

13.1.9. CLKOUT output register (Reg

-

0D

[h])

Address

[h]

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

0D

CLKOUT frequency

FE

Ч

Ч

Ч

Ч

Ч

FD1

FD0

•

This register is used to control clock output via the CLKOUT output pin.

•

This register is valid only when the CLKOE input pin is at high level, at which time clock output is enabled or

disabled (stopped) depending on the settings in this register.

∗

When the CLKOE input pin is at low level, CLKOUT is at low level regardless of the settings in this register.

1) FE bit

(

Frequency output

Enable

)

When this register is valid (when CLKOE is at high level), it is used to control the CLKOUT pin's output

status.

When the FE bit value is "1", the CLKOUT pin is in output mode. The content being output at that time is

the frequency specified via the FD1 and FD0 bit.

When the FE bit value is "0", the CLKOUT pin is output STOP mode (= low level).

2) FD1,

FD0 bits

A combination of the FD1 and

FD0 bits is used to select the frequency to be output.

3) CLKOUT output based on various settings

CLKOE pin

input

FE

bit

FD1

bit

FD0

bit

CLKOUT pin

output

0

0

32768

Hz

Output

(

C-MOS

)

0

1

1024

Hz

Output

(

C-MOS

)

1

0

32

Hz

Output

(

C-MOS

)

1

1

1

1

Hz

Output

(

C-MOS

)

"

H

"

0

Χ

Χ

OFF

(

"

L

"

)

1

Χ

Χ

OFF

(

"

L

"

)

"

L

"

0

Χ

Χ

OFF

(

"

L

"

)

Χ

: don't care

∗

During initial power-on (from 0 V), "1" is set to the FE bit by the power-on reset function, and the FD1

and FD0 bits are reset to zero.

Consequently, 32.768

kHz output can be obtained from the CLKOUT output pin by setting the CLKOE

input pin to high level.

Note) Re: CLKOUT output operation when STOP bit value is "1"

Note with caution that when the STOP bit value is

"1", output via CLKOUT may be stopped, depending on

the selected frequency.

(1) When 32.768

kHz output has been selected, output continues at 32.768

kHz.

(2) When any other frequency has been set (1024Hz,

32Hz,

or 1Hz), CLKOUT output is stopped.