ELANsat Tech OTP ROM EM78P156N User Manual

Page 33

EM78P156N

OTP ROM

EM78P156N

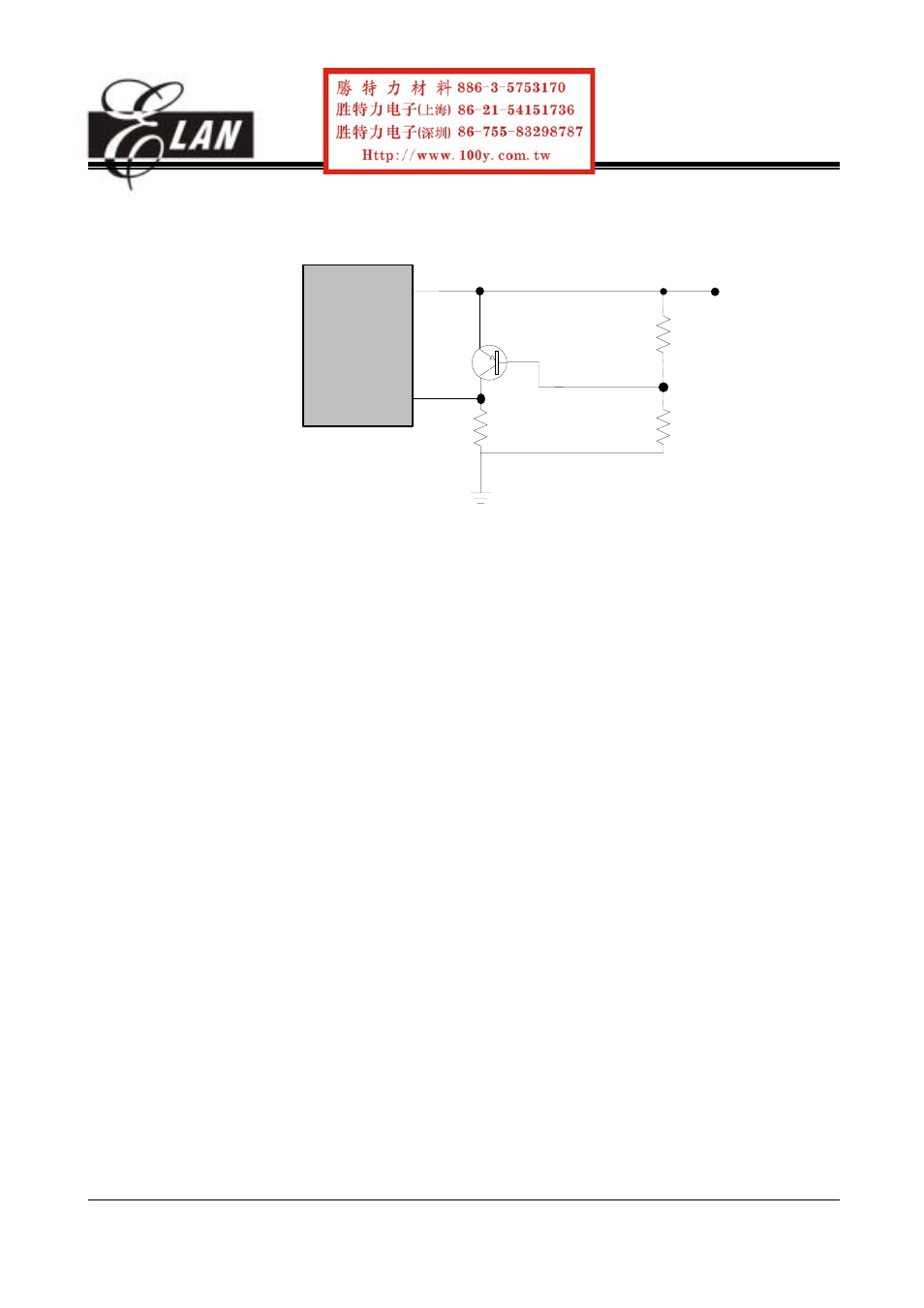

/RESET

Vdd

Q1

Vdd

40K

R2

R1

Fig. 16 Circuit 2 for the Residue Voltage Protection

4.12 Instruction Set

Each instruction in the instruction set is a 13-bit word divided into an OP code and one or more operands.

Normally, all instructions are executed within one single instruction cycle (one instruction consists of 2

oscillator periods), unless the program counter is changed by instruction "MOV R2,A", "ADD R2,A", or by

instructions of arithmetic or logic operation on R2 (e.g. "SUB R2,A", "BS(C) R2,6", "CLR R2",

⋅⋅⋅⋅). In this case,

the execution takes two instruction cycles.

If for some reasons, the specification of the instruction cycle is not suitable for certain applications, try

modifying the instruction as follows:

(A) Change one instruction cycle to consist of 4 oscillator periods.

(B) "JMP", "CALL", "RET", "RETL", "RETI", or the conditional skip ("JBS", "JBC", "JZ", "JZA", "DJZ",

"DJZA") commands which were tested to be true, are executed within two instruction cycles.

The instructions that are written to the program counter also take two instruction cycles.

Case (A) is selected by the CODE Option bit, called CLK. One instruction cycle consists of two oscillator clocks

if CLK is low, and four oscillator clocks if CLK is high.

Note that once the 4 oscillator periods within one instruction cycle is selected as in Case (A), the internal clock

source to TCC should be CLK=Fosc/4, instead of Fosc/ 2 as indicated in Fig. 5.

In addition, the instruction set has the following features:

(1) Every bit of any register can be set, cleared, or tested directly.

This specification is subject to change without prior notice. 33

07.29.2004 (V1.2)

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW

WW

W.100

Y.COM.TW