Tms320c6416t – Sundance SMT395 User Manual

Page 8

Version 1.1.7

Page 8 of 26

SMT395 User Manual

TMS320C6416T

The processor will run with zero wait states from internal SRAM.

An on-board crystal oscillator provides the clock used for the C60, which then

multiplies this by 12 internally.

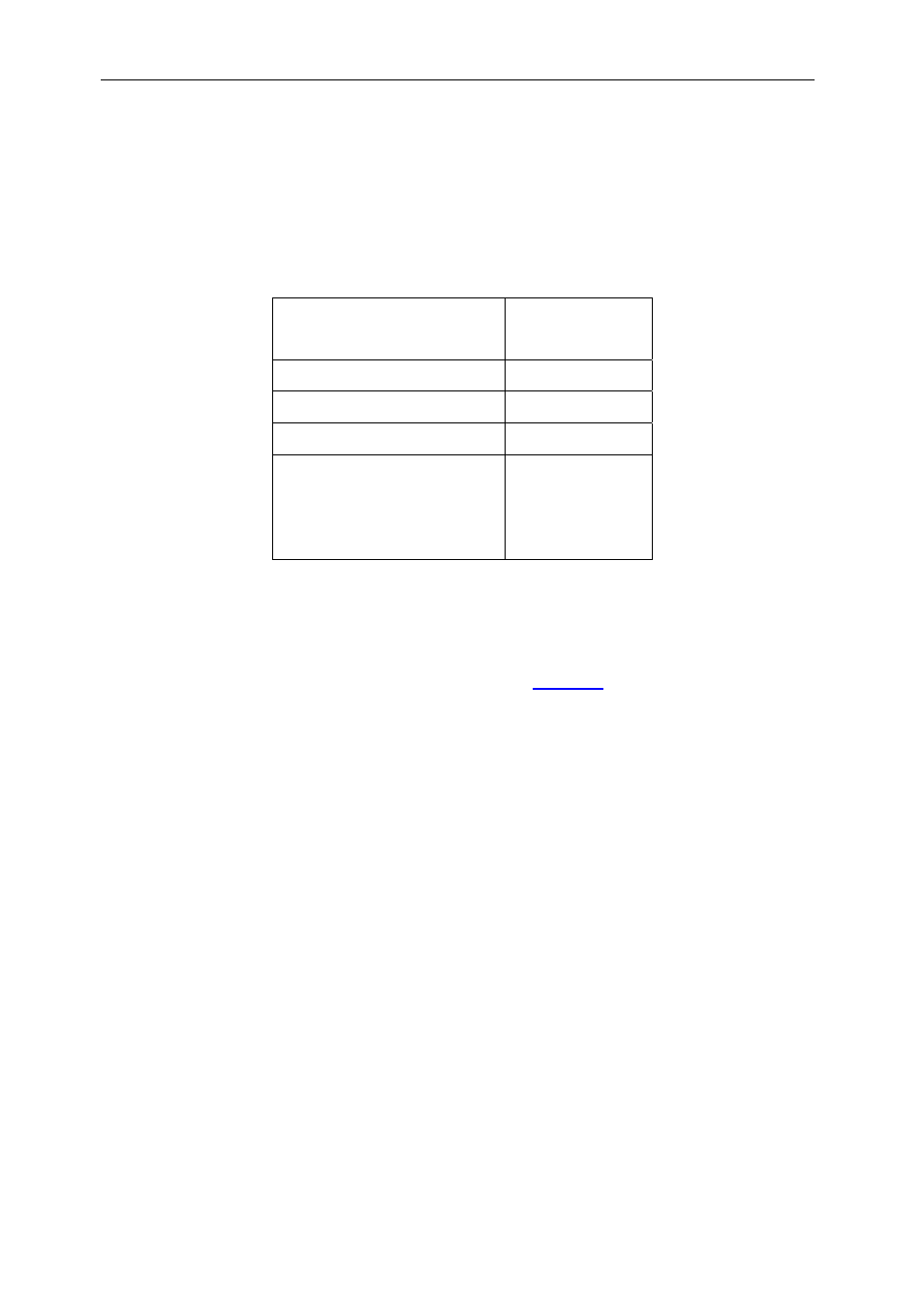

The following table shows the main DSP characteristics.

Feature C6416T

DMA / McBSP / Timer

64/3/3

On-chip memory

1056k bytes

Speed 1GHz

Others UTOPIA

Viterbi and

Turbo

decoders

The SMT395 implementation using this DSP provides interfaces using the EMIFs

(External Memory Interfaces A & B), timers and JTAG.

The JTAG interface is provided to enable application debugging via a suitable JTAG

controller and software. Typically, this will be an

SMT310

and TI Code Composer

Studio. This is an invaluable interface which enables the application programmer to

quickly debug a ‘chain’ of processors in single or multi-processor situations.

The EMIFA is used to connect to a 133MHz, 256Mbyte bank of SDRAM (4 devices of

64M bytes, Samsung K4S511632M-TC75), and the VirtexII-Pro.

The flash is connected via EMIFB as a 16 bit device. The EMIFA supplies 4 ‘chip

selects’ which are used for these selections.