Sundance FC203B User Manual

Page 7

Page 7 of 7

Revision 0.5

Sundance Digital Signal Processing Inc.

4790 Caughlin Parkway 233, Reno, NV 89519-0907, U.S.A.

Tel: +1 (775) 827-3103, Fax: +1 (775) 827-3664, email:

www.sundancedsp.com

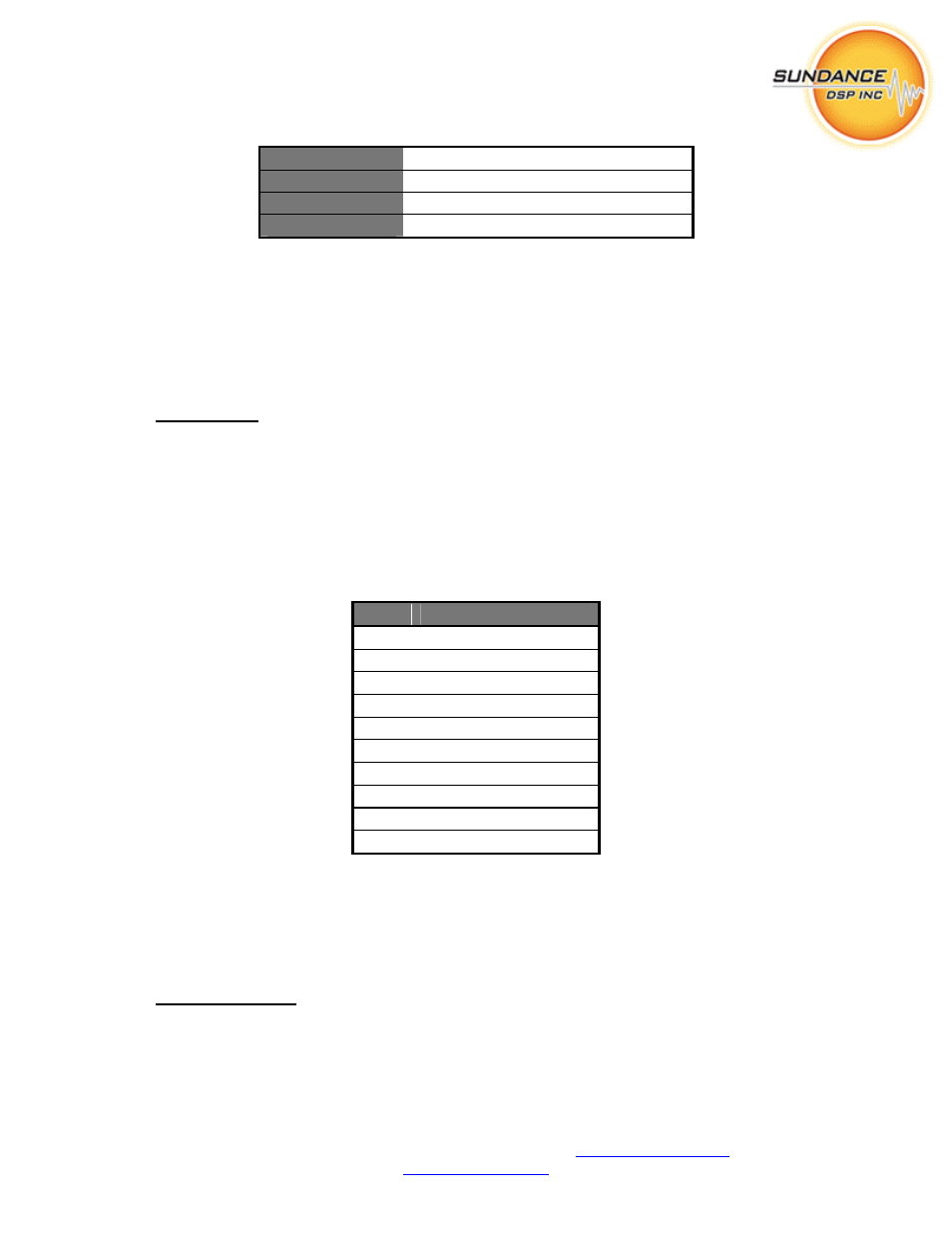

Enable = xxx1b

F0_IN inserted at channels 0 & 1

Enable = xx1xb

F1_IN inserted at channels 2 & 3

Enable = x1xxb

F2_IN inserted at channels 4 & 5

Enable = 1xxxb

F3_IN inserted at channels 6 & 7

Table 5 – Enable Configuration

For channels which are not enabled (corresponding bit is clear) and which are within the current

value of C from FDMA_CM_IN, the data placed on FDMA_OUT will be set to zero.

NOTE: To simplify the FPGA logic, the control word is assumed to be static while the module is

enabled. Changes to SPAN while any ENABLE bit is set will result in unpredictable output.

FDMA_OUT

This is a multi-channel frequency domain highway. Data values are groups of C 32-bit values

inside M micro-frames. The 32-bit values consist of the in-phase and quadrature components

(16-bit twos-complement as described in the FC108 User Manual) of one channel packed into a

32-bit word. The micro-frame represents one frequency bin of C channels, while the frame

represents M frequency bins as configured by port FDMA_CM_IN. This port is suitable for

connecting to any FDMA_IN port.

Word Bits 31..16

Bits 15..0

0 AQ(0) AI(0)

1 BQ(0) BI(0)

2 CQ(0) CI(0)

3 AQ(1) AI(1)

4 BQ(1) BI(1)

5 CQ(1) CI(1)

… …

…

3M-3

AQ(M-1) AI(M-1)

3M-2

BQ(M-1) BI(M-1)

3M-1

CQ(M-1) CI(M-1)

Table 6 - FDMA Data Organization, C=3

When any of the ENABLE bits are set, this module will generate data as soon as a full micro-

frame’s worth of input has been received on all active input channels, and obeys the ‘Ready’

signal from the downstream module.

FDMA_CM_OUT

This port describes the current configuration of the FDMA_OUT port. See the description for

FDMA_CM_IN, above. It is suitable for connection to any FDMA_CM_IN port.