Sundance FC203B User Manual

Page 6

Page 6 of 6

Revision 0.5

Sundance Digital Signal Processing Inc.

4790 Caughlin Parkway 233, Reno, NV 89519-0907, U.S.A.

Tel: +1 (775) 827-3103, Fax: +1 (775) 827-3664, email:

www.sundancedsp.com

F0_IN .. F3_IN

These are dual-channel partitioned frequency data ports. Data values are groups of 64-bit values

in bursts of SPAN qwords. The 64-bit values consist of the in-phase and quadrature components

(16-bit two’s complement as described in the FC108 User Manual) of two channels. This port is

suitable for connecting to the Fx_OUT ports of the FC203A subcomponent.

Bit 15..0

I0(0) I0(1) … I0(SPAN

–

1)

Bit 31..16

Q0(0) Q0(1) … Q0(SPAN – 1)

Bit 47..32

I1(0) I1(1) … I1(SPAN

–

1)

Bit 63..48

Q1(0) Q1(1) … Q1(SPAN – 1)

Table 3 – Stream Format of Fx_IN Port, low-frequency channel, LOW_FREQ = 0

NOTE: The FC203B module has 1024 samples worth of internal buffering on each of the 4

inputs (a sample includes one in-phase and one quadrature value). The system design must

insure that this is sufficient to handle the worst-case combination of lag between any pair of

channels, PLUS the worst-case latency of the FDMA_OUT output sink. A FIFO at the

FDMA_OUT port may help with output latency, but FIFOs will not help between the FC203A

and FC203B because the inputs to FC203B are “always ready.”

CTRL_IN

Control miscellaneous parameters and features of the FC203B subcomponent. The port accepts

data one 32-bit word at a time. The bit definitions are compatible with the definition used in the

FC203A module.

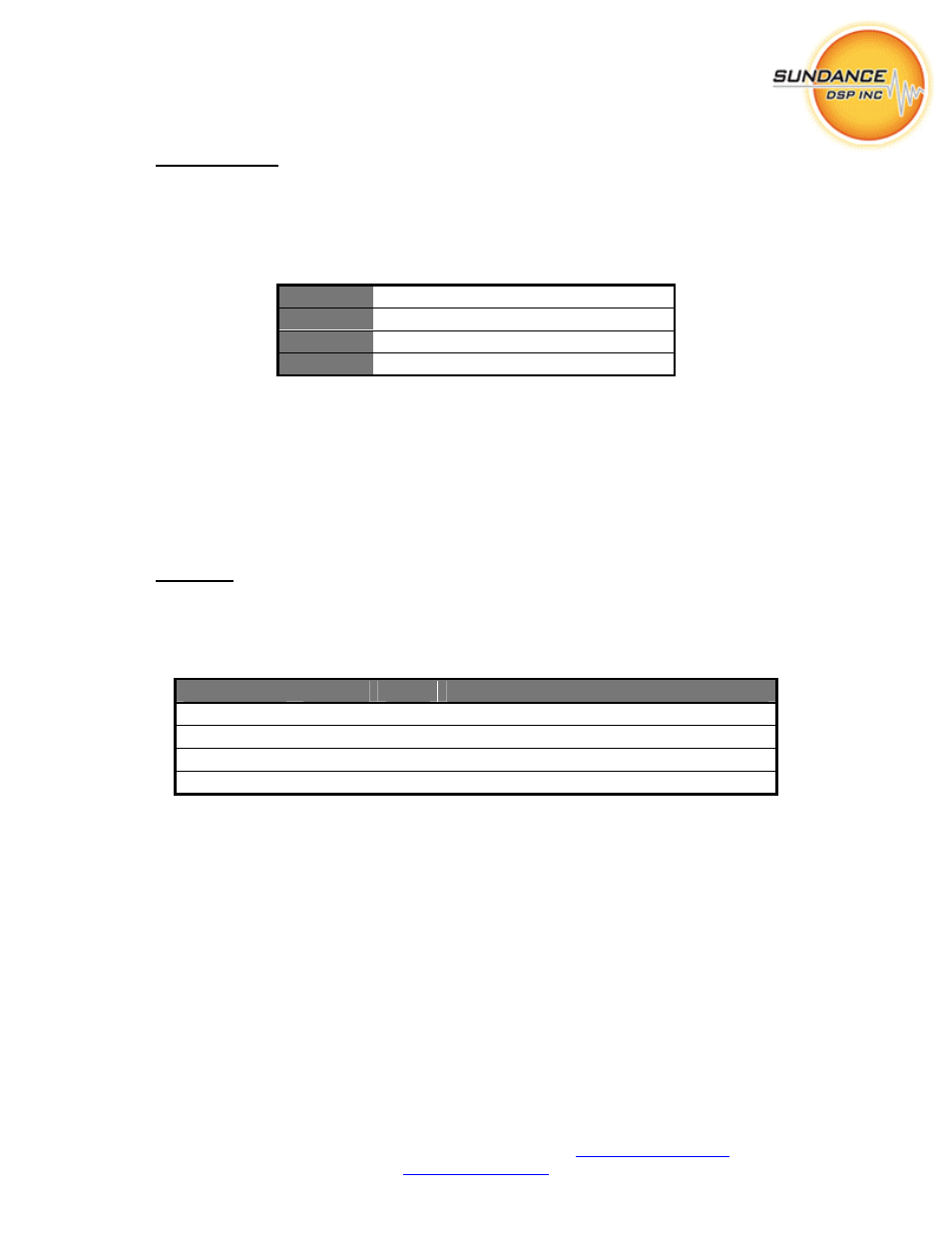

Signal

Bits

Mode Description

RESERVED 15..lsb R/W Pass-through

(reserved)

SPAN

25..16

R/W

Select number of active frequency bins

RESERVED 27..26 R/W Pass-through

(reserved)

ENABLE msb..28

R/W

Channel-pair

enable

Table 4 - FC203B Control Word

The FC203B module ignores some of the bits; they exist to enable the configuration of multiple

modules (including FC203A) in a daisy-chain fashion. SPAN determines the number of

frequency bins that are present in the inbound Fx_IN streams. SPAN must be less than or equal

to M (from FDMA_CM_IN). ENABLE determines how many of the Fx_IN streams are to be

packaged on the FDMA_OUT sequence. Each bit in the ENABLE control word allows the

corresponding Fx_IN stream to be inserted into the output. Enables occur according to the

following pattern: