Measurement Computing PCI-DIO96 User Manual

Page 16

PCI-DIO96 User's Guide

Functional Details

16

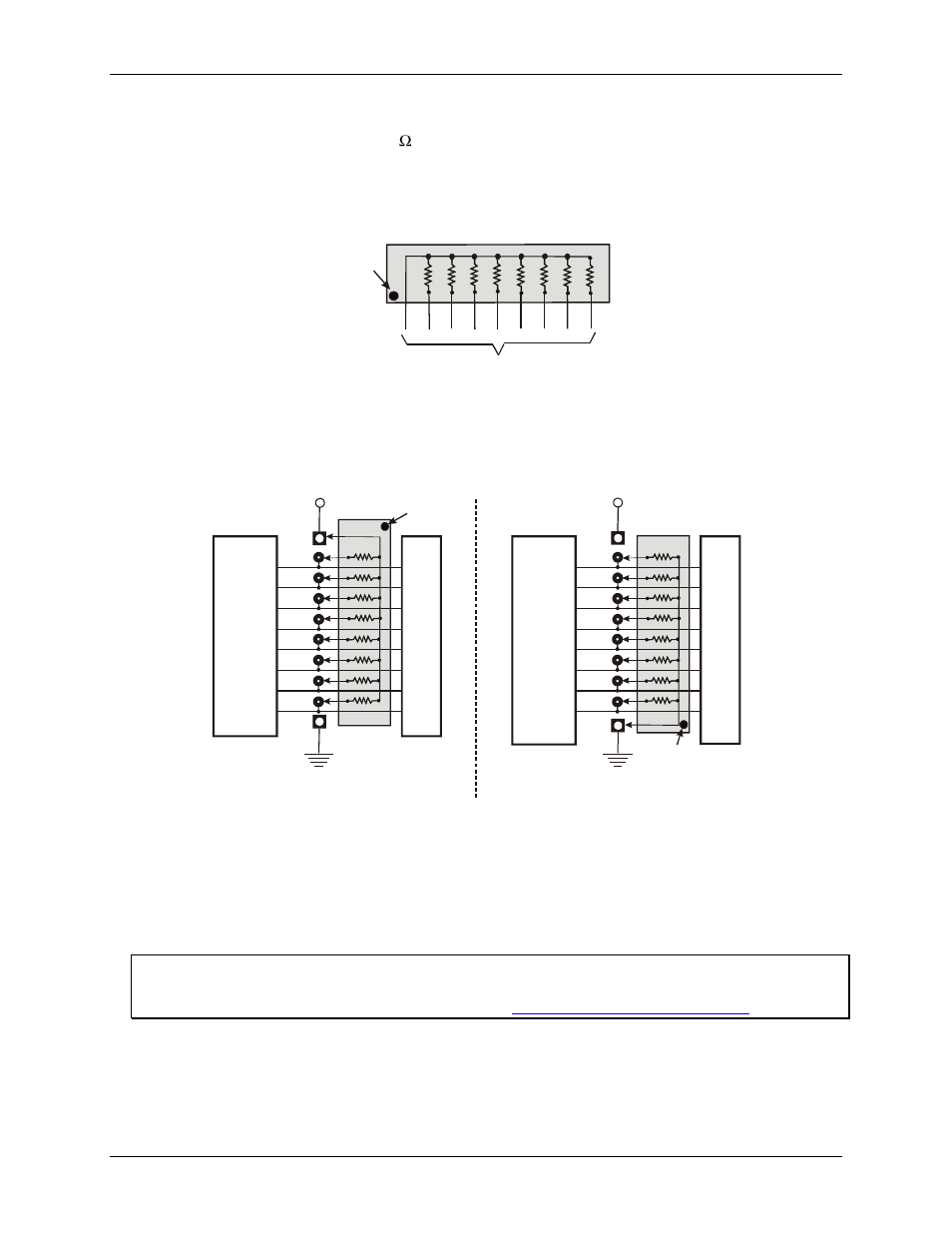

To safeguard against unwanted signal levels, the devices being controlled by PCI-DIO96 series boards should

be tied low or high as required by a 2.2K resistor. In a 2.2K eight-resistor SIP pack, one side of all of the

resistors is connected to a single common point and brought out to a pin. The common line, usually marked

with a dot or line, is at one end of the SIP. The remaining resistor ends are brought out to the other eight pins

(refer to Figure 5).

2.2KOhm SIP

Dot indicates the

common line

(LO or HI)

I/O Lines

Figure 5. Eight-resistor SIP schematic

Figure 6 shows a schematic of an SIP installed in both the pull-up and pull-down positions. Each port provides

10 holes in a line. The end labeled

HI

connects to +5V. The end marked

LO

connects to GND. The eight holes

in the middle (n0 –n7) connect to the eight lines of the Port, A, B or C.

2.2 K SIP installed for pull-up

2.2 K SIP

Dot

+ 5 VDC

HI

LO

(GND)

n7

U

s

e

r

C

o

n

n

e

c

to

r

D

ig

it

a

l

I/

O

L

in

e

s

n5

n4

n3

n2

n1

n0

n6

COM

Digital

I/O

Port

n = A, B, or C

2.2 K SIP

Dot

+ 5 VDC

HI

LO

(GND)

n7

U

s

e

r

C

o

n

n

e

c

to

r

D

ig

it

a

l

I/

O

L

in

e

s

n5

n4

n3

n2

n1

n0

n6

COM

2.2 K SIP installed for pull-down

Digital

I/O

Port

n = A, B, or C

Figure 6. Pull-up and pull-down resistor SIPs schematic

To pull-up lines, orient the SIP with the common pin (dot) toward the

HI

end; to pull-down, install the resistor

with the common pin in the

LO

hole.

When installing pull-up and pull-down resistor SIP packs, we recommend using 2.2K, eight-resistor Single

Inline Packages (MCC part number SP-K2.29C). Use a different value only if necessary.

Information on signal connections

General information regarding signal connection and configuration is available in the Guide to Signal

Connections. This document is available on our web sit