Pci-dio48h block diagram – Measurement Computing PCI-DIO48H User Manual

Page 8

PCI-DIO48H User's Guide

Introducing the PCI-DIO48H

8

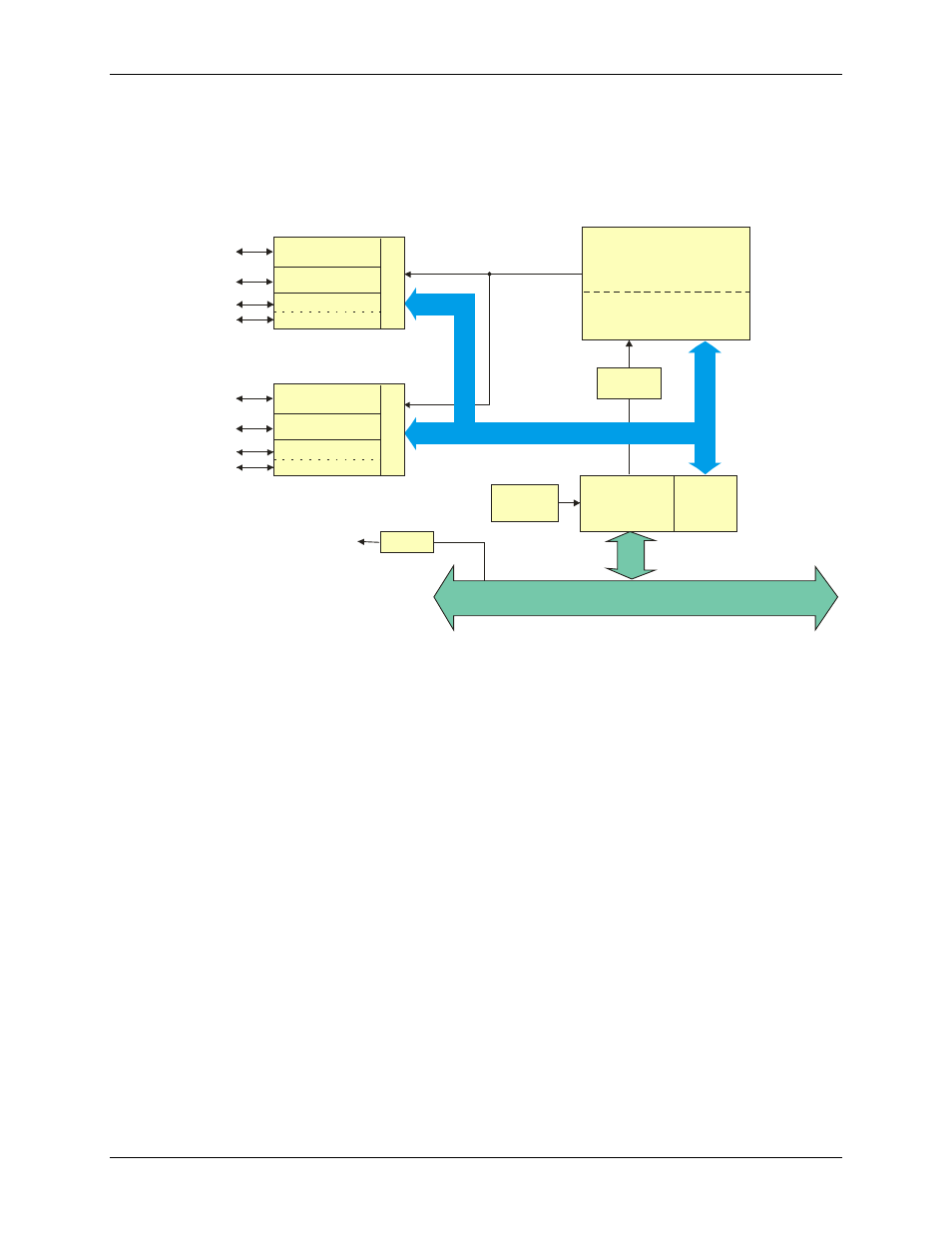

PCI-DIO48H block diagram

PCI-DIO48H functions are illustrated in the block diagram shown here.

PCI BUS (5V, 32-bit, 33 MHz)

PCI

Controller

BADR2

Boot

EEPROM

Control

Registers

Decode/Status

Controller CPLD and Logic

Local Bus

Control Bus

Bus

Timing

FIRSTPORTA

FIRSTPORTB

C

o

n

tr

o

l

FIRSTPORTCH

SECONDPORTA

SECONDPORT B

C

o

n

tr

o

l

HIGH DRIVE

SECONDPORT

FIRSTPORTA(7:0)

FIRSTPORTB(7:0)

FIRSTPORTCH(3:0)

FIRSTPORTCL(3:0)

FIRSTPORTCL

SECONDPORTA(7:0)

SECONDPORT B(7:0)

SECOND PORTCH(3:0)

SECONDPORTCL(3:0)

SECONDPORT CH

SECONDPORT CL

HIGH DRIVE

FIRSTPORT

Fuse

+5V User Output

+5V

Figure 1. PCI-DIO48H block diagram

See also other documents in the category Measurement Computing Hardware:

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16-I (16 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS800 (20 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DAS-TEMP (20 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24H (20 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)