Wait state jumper, Individual / simultaneous update jumper – Measurement Computing CIO-DAC08 User Manual

Page 11

CIO-DAC08 User's Guide

Installing the CIO-DAC08

Wait state jumper

The CIO-DAC08 board has a wait state jumper which you can set to enable an on-board wait state generator.

A wait state is an extra delay injected into the processor's clock via the bus. This delay slows down the

processor when the processor addresses the CIO-DAC08 board so that signals from slow devices (chips) will

be valid.

configured for OFF (wait state is disabled).

Figure 2. Wait State jumper

ON

OFF

The wait state generator on the CIO-DAC08 is only active when the CIO-DAC08 is being accessed. Your PC

will not be slowed down in general by using the wait state.

Individual / simultaneous update jumper

The analog output chips on the CIO-DAC08 are dual DACs (two analog outputs per chip). Each DAC channel

pair has an associated jumper that sets both DACs on a single chip to be either simultaneously transferred on a

read (XFER), or individually updated when the MSB register is written.

The top of each jumper on the CIO-DAC08 board is labeled

XFER

. Below each jumper are two numbers that

indicate the pair of channels that the jumper selects (12, 34, 56, or 78). For example, "12" indicates channels

one and two.

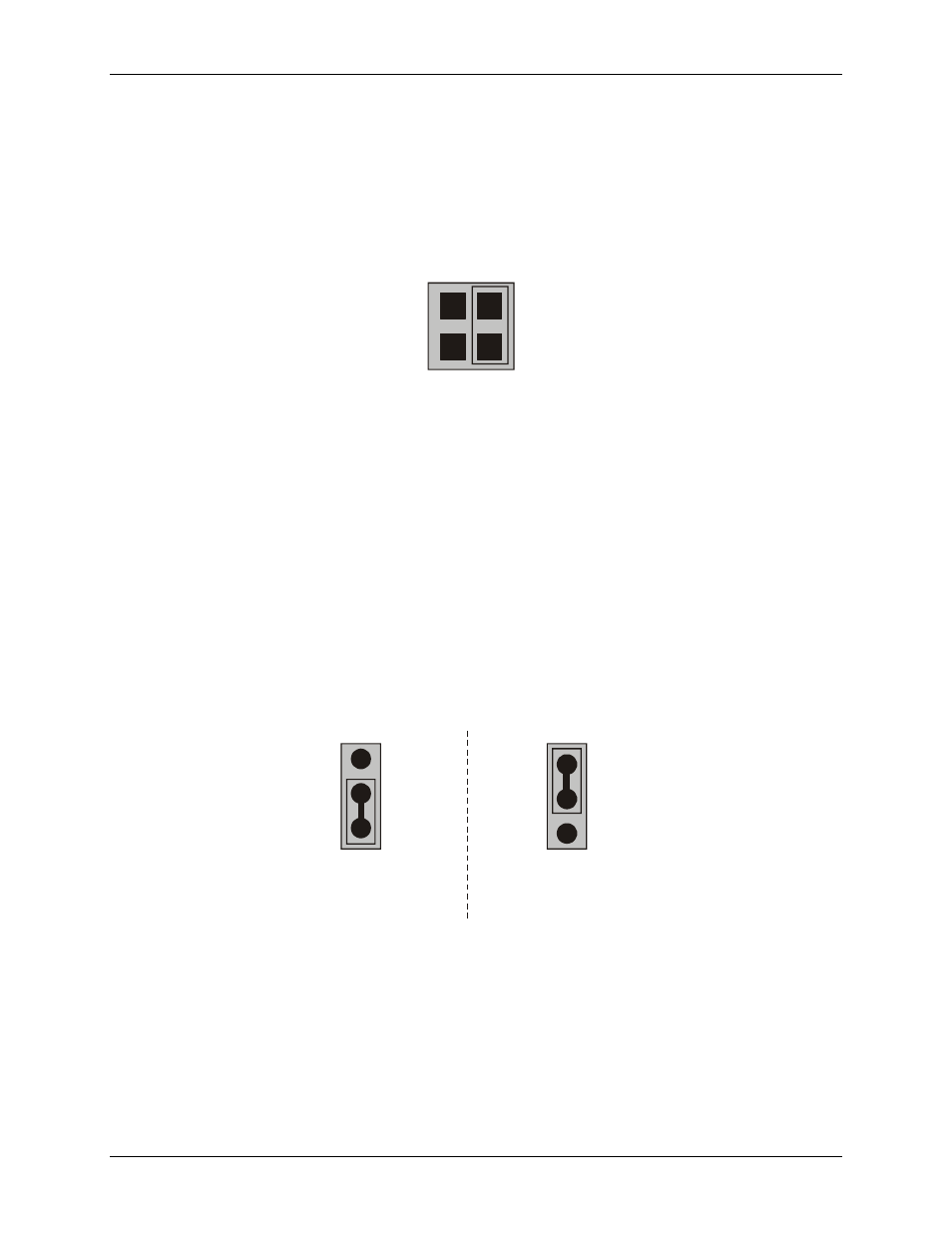

Figure 3. Individual / simultaneous update jumper

shows the jumper block configured for each update mode.

XFER

# #

(Update)

Individual updates

per DAC

(two channels)

XFER

# #

(Update)

Simultaneous updates

from all DACS

jumpered to XFER

When the jumpers are in the

XFER

position, new output data is held until one or more DACs have been

loaded with new digital data. The new data transfers to the voltage outputs as a group. The simultaneous

transfers occur when any of the CIO-DAC08 addresses are read (and the jumpers are in the

XFER

position).

When jump

ered to the channel numbers, the DAC channel pair is individually updated.

11