Spi interface, Spi signals, Reference schematic – IBASE SMARC Evaluation Kit User Manual

Page 46

20

SMARC Evaluation Kit

4.2.14. SPI Interface

SPI Signals

Pin

Signal Name

I/O

Type

Power Rail

Description

P43

CSPI1_CS0#

O

CMOS

3.3V

SPI1 Master Chip Select 0 output

P31

CSPI1_CS1#

O

CMOS

3.3V

SPI1 Master Chip Select 1 output

P44

CSPI1_CLK

O

CMOS

3.3V

SPI1 Master Clock output

P45

CSPI1_MISO

I

CMOS

3.3V

SPI1 Master Data input

P46

CSPI1_MOSI

O

CMOS

3.3V

SPI1 Master Data output

Pin

Signal Name

I/O

Type

Power Rail

Description

P54

CSPI2_CS0#

O

CMOS

3.3V

SPI2 Master Chip Select 0 output

P55

CSPI2_CS1#

O

CMOS

3.3V

SPI2 Master Chip Select 1 output

P56

CSPI2_CLK

O

CMOS

3.3V

SPI2 Master Clock output

P57

CSPI2_MISO

I

CMOS

3.3V

SPI2 Master Data input

P58

CSPI2_MOSI

O

CMOS

3.3V

SPI2 Master Data output

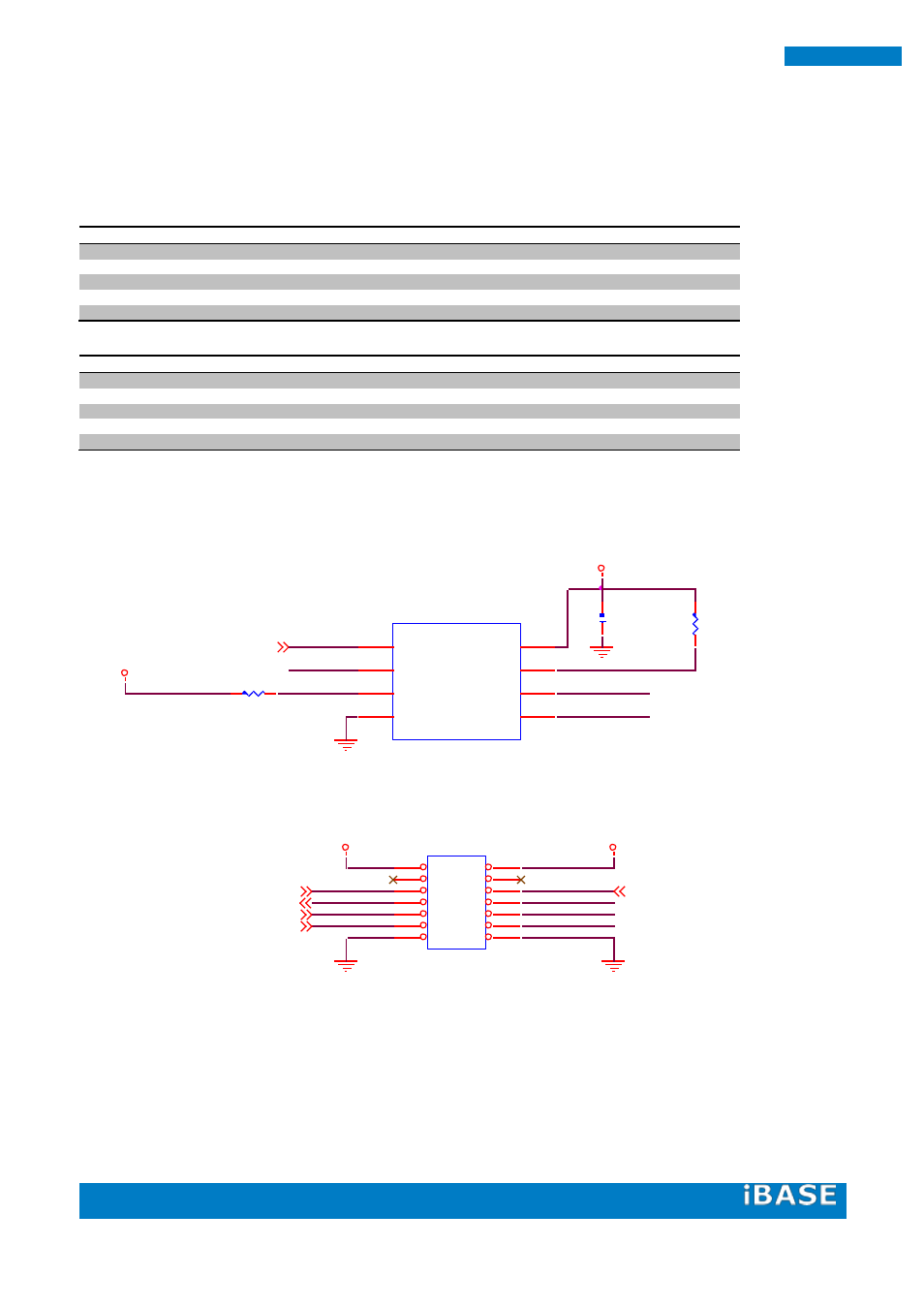

Reference Schematic

CSPI1_CS0#

13

CSPI1_CLK

CSPI1_MOSI

CSPI2_MOSI

CSPI2_CLK

CN7

E-CALL_0196-01-251-140

1

2

3

4

5

6

7

8

9

10

11

12

13

14

CSPI2_MISO

+3.3V_VCC

+3.3V_VCC

CSPI1_CLK

13

CSPI1_CS1#

13

+3.3V_VCC

CSPI1_MISO

13

CSPI1_MISO

CSPI1_MOSI

13

CSPI1_CLK

CSPI1_MISO

+3.3V_VCC

CSPI2_CS1# 13

CSPI1_MOSI

C59

0.1UF/25V/4

U9

W25Q32FV

HOLD#

7

SCK

6

SI

5

CE#

1

SO

2

VSS

4

WP#

3

VDD

8

R51

10K/4

R49

10K/4