Serial camera interface, Serial camera signals, Reference schematic – IBASE SMARC Evaluation Kit User Manual

Page 39: Ibase technology inc

Copyright © 2013 IBASE Technology Inc. All Rights Reserved.

13

IBASE Technology Inc.

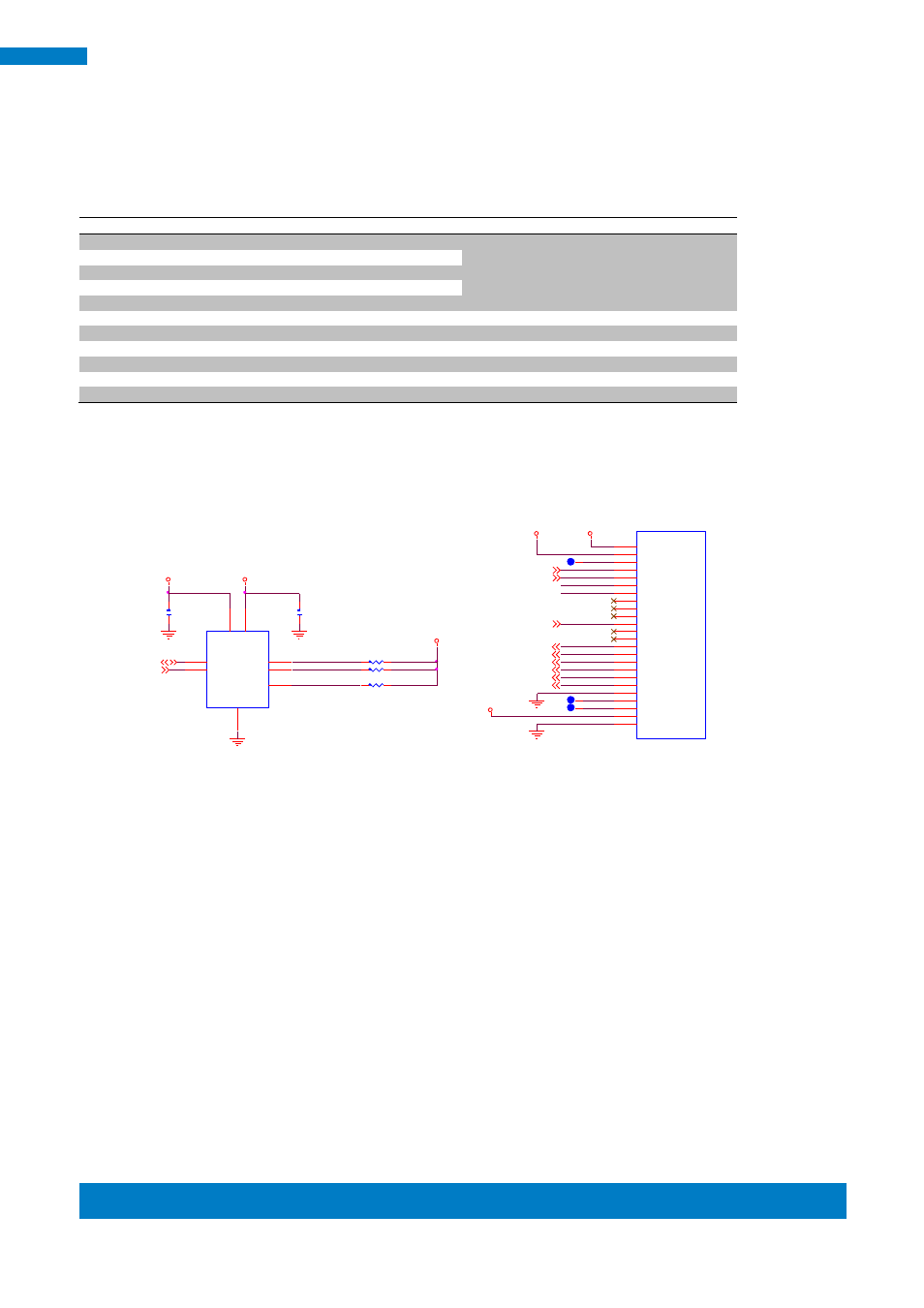

4.2.7. Serial Camera Interface

Serial Camera Signals

Pin

Signal Name

I/O

Type

Power Rail

Description

S8

CSI_CLK0P

I

LVDS D-PHY

CSI clock

S9

CSI_CLK0M

I

LVDS D-PHY

S11

CSI_D0P

I

LVDS D-PHY

CSI data lane 0

S12

CSI_D0M

I

LVDS D-PHY

S14

CSI_D1P

I

LVDS D-PHY

CSI data lane 1

S15

CSI_D1M

I

LVDS D-PHY

S6

CSI_MCLK

O

CMOS

3.3V

Master clock output for CSI camera

S5

I2C2_CLK

O

OD

3.3V

I2C clock

S7

I2C2_SDA

I/O

OD

3.3V

I2C data

P108

CAM0_PWR#

O

CMOS

3.3V

Camera Power Enable

P110

CAM0_RST#

O

CMOS

3.3V

Camera Reset

Reference Schematic

CAM_SDA

CAM_SCL

TP3

+1.8V_VCC

R240

1K/4

TP4

R241

1K/4

CSI_D0M

13

CSI_D0P

13

C41

0.1UF/25V/4

J3

TECHBEST_7080K-F24N-24R

AVDD(2.8V)

1

DVDD(1.5V/NC)

3

DOVDD(2.8V/1.8V)

2

MCLK

4

PWDNh

5

SCL

6

SDA

7

PCLK

8

VSY NC

9

HSY NC

10

D2

12

RESETn

11

D3

13

D4/MDN0

14

D5/MDP0

15

D6/MCN

16

D7/MCP

17

D8/MDN1

18

D9/MDP1

19

GND

20

STROBE

21

FREX

22

VCM_VDD(2.8V)

23

VCM_GND

24

CSI_CLK0P

13

CSI_CLK0M

13

CSI_D1P

13

CSI_D1M

13

C42

0.1UF/25V/4

U6

TXS0102DCTR

OE

6

B2

1

B1

8

VC

C

B

7

VC

C

A

3

A1

5

A2

4

GN

D

2

CAM0_RST#

13

I2C2_SCL

8,13

+2.8V_VCC

+2.8V_VCC

I2C2_SDA

8,13

CSI_MCLK

13

CAM0_PWR#

13

CAM_SCL

CAM_SDA

+1.8V_VCC

R242

1K/4

+3.3V_VCC

TP2

+1.8V_VCC