Lvds lcd interface, Lvds lcd signals, Reference schematic – IBASE SMARC Evaluation Kit User Manual

Page 37: Ibase technology inc

Copyright © 2013 IBASE Technology Inc. All Rights Reserved.

11

IBASE Technology Inc.

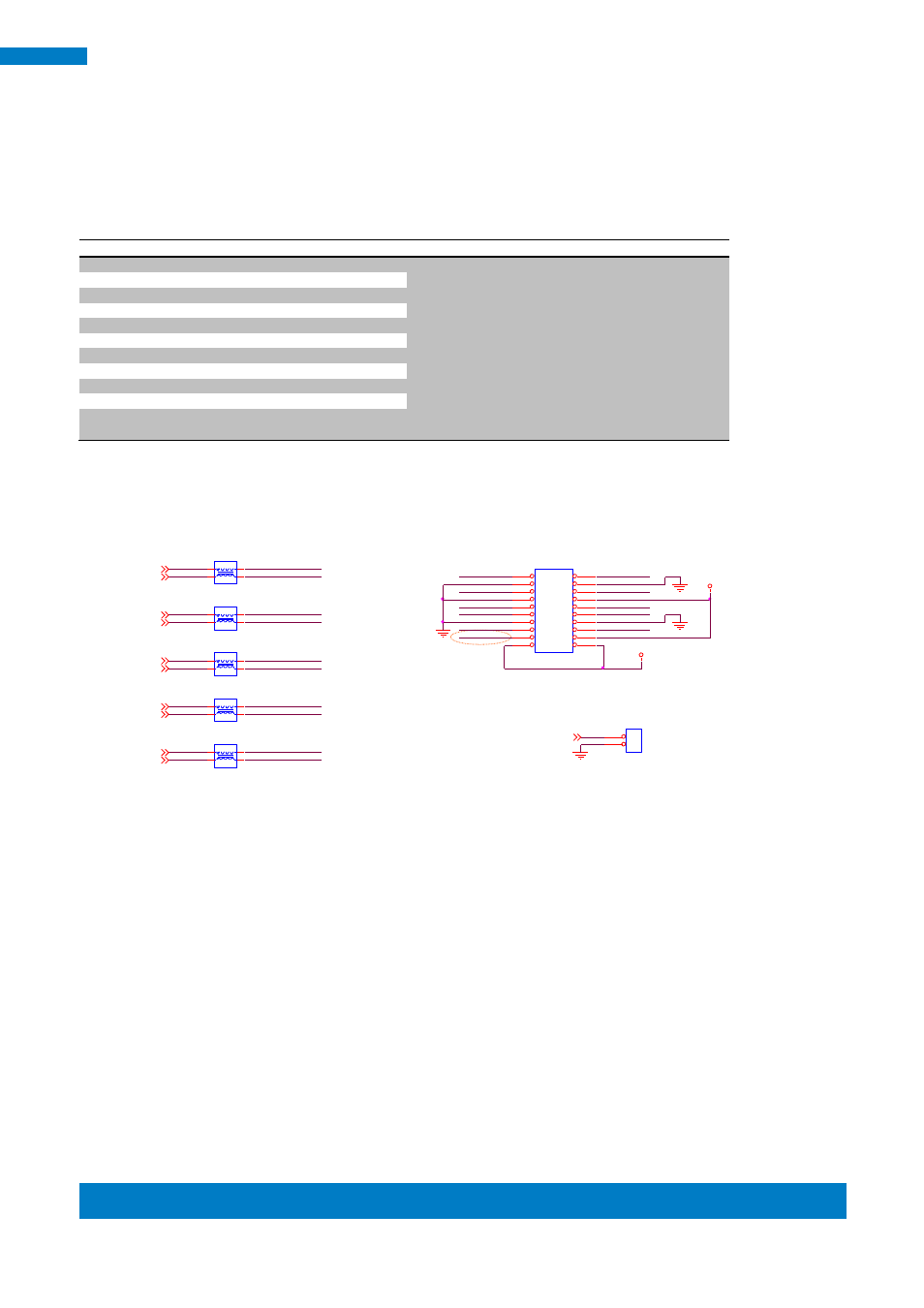

4.2.5. LVDS LCD Interface

LVDS LCD Signals

Pin

Signal Name

I/O

Type

Power Rail

Description

S134

LVDS0_CLK_P

O

LVDS

LVDS clock

S135

LVDS0_CLK_N

O

LVDS

S125

LVDS0_TX0_P

O

LVDS

LVDS data lane 0

S126

LVDS0_TX0_N

O

LVDS

S128

LVDS0_TX1_P

O

LVDS

LVDS data lane 1

S129

LVDS0_TX1_N

O

LVDS

S131

LVDS0_TX2_P

O

LVDS

LVDS data lane 2

S132

LVDS0_TX2_N

O

LVDS

S137

LVDS0_TX3_P

O

LVDS

LVDS data lane 3

S138

LVDS0_TX3_N

O

LVDS

S142

LCD_DUAL_PCK

O

LVDS

Pixel clock to support dual channel parallel and LVDS

implementations

Reference Schematic

LM4

ACM2012H-900-2P

2

3

1

4

LM2

ACM2012H-900-2P

2

3

1

4

LM3

ACM2012H-900-2P

2

3

1

4

BKLT_VCC

LM1

ACM2012H-900-2P

2

3

1

4

LVDS0_TX0_P

13

LVDS_TX1-

LVDS_TX1+

LCD_DUAL_PCK

13

LVDS_TX2-

LVDS_TX2+

LVDS_TX3-

LVDS_TX3+

LM5

ACM2012H-900-2P

2

3

1

4

LVDS0_TX0_N

13

LCD_VDD

BTL_PWM

CN9

HRS_DF13-20DP-1.25V(95)

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

LVDS_CLK-

LVDS_CLK+

LVDS0_TX1_N

13

LVDS0_TX1_P

13

LVDS_TX0-

LVDS_TX0+

CN3

E-CALL_0195-01-200-020

1

1

2

2

LVDS0_TX3_P

13

LVDS0_TX2_N

13

LVDS0_TX2_P

13

LVDS0_TX3_N

13

LVDS_TX0+

LVDS_TX0-

LVDS0_CLK_P

13

LVDS0_CLK_N

13

LVDS_TX1+

LVDS_TX3-

LVDS_TX3+

LVDS_TX2-

LVDS_TX2+

LVDS_TX1-

LVDS_CLK-

LVDS_CLK+