U macro-cpu hardware memory map – Delta Tau MACRO CPU BOARD 4Ax-602804-xHxx User Manual

Page 32

MACRO-CPU Hardware Reference

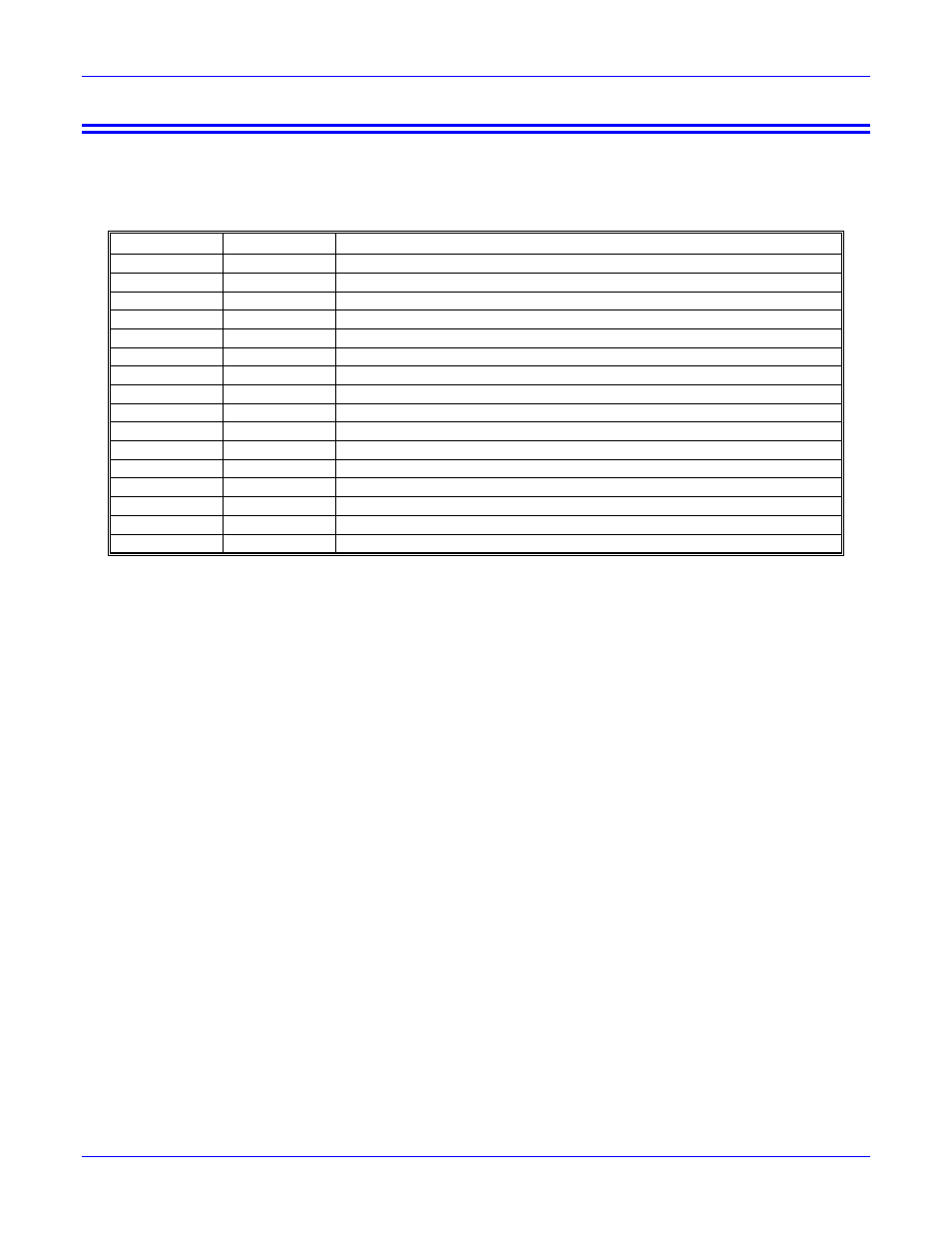

U MACRO-CPU HARDWARE MEMORY MAP

The values in this table represent the hardware locations associated with register-based transactions that occur in

the 3U MACRO-CPU.

Reference ADDR

(hex)

Description

CS00-

$FFC0

Stack I/O select #1

CS02-

$FFC8

Stack I/O select #2

CS04-

$FFD0

Stack I/O select #3

CS06-

$FFD8

Stack I/O select #4

CS0-

$C000

Stack axis 1-4 select

CS1-

$C020

Stack axis 5-8 select

CS2-

$C040

UBUS backplane axis 1-8 select

CS3-

$C060

UBUS backplane axis 5-8 select

CS4-

$C080

On-board DSPGATE2 select

CS4X-

$C0C0

UBUS backplane MACROgate or DSPgate2 select (CS4- on UBUS)

CS10-

$FFE0

UBUS backplane I/O select #1

CS12-

$FFE8

UBUS backplane I/O select #2

CS14-

$FFF0

UBUS backplane I/O select #3

CS16-

$FFF8

UBUS backplane I/O select #4

MEMCS0-

$D000

UBUS hardware I/O field (was DPRCS-)

MEMCS1-

$E000

UBUS hardware I/O field (was VMECS-)

The addressing field size is 16-bits in the 3U MACRO-CPU. The address table above is similar to the PMAC2

product line.

U MACRO-CPU Hardware Memory Map

28