Chapter 3 – DFI OT905-B series User Manual

Page 20

www.dfi .com

Chapter 3 Hardware Installation

20

Chapter 3

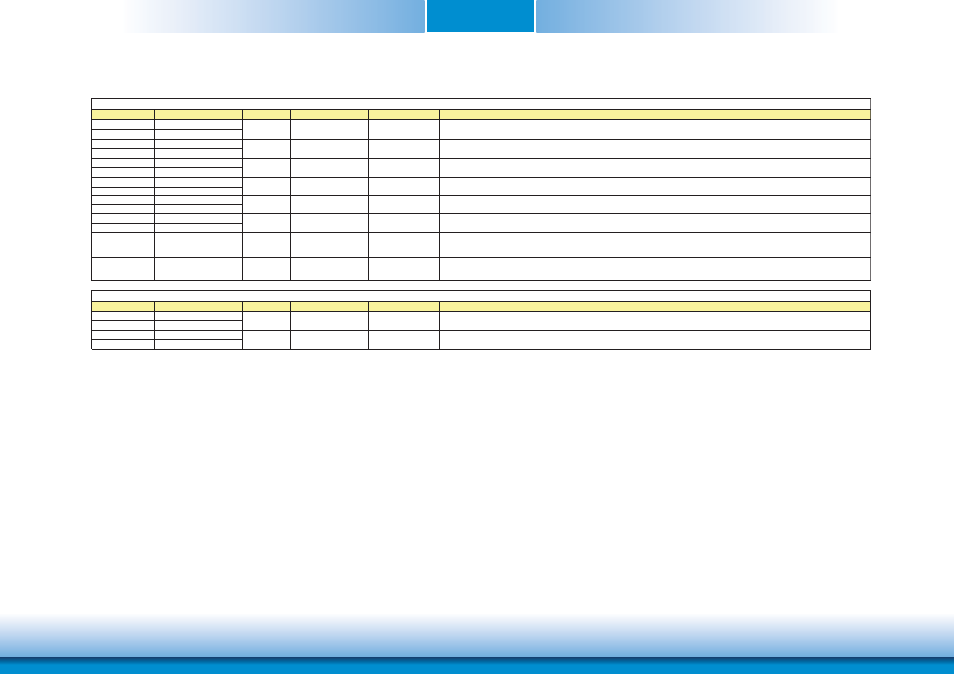

Signal

Pin#

Pin Type

Pwr Rail /Tolerance

PU/PD

Description

PEG Signals Descriptions

PEG_TX13+

D94

PEG_TX13-

D95

PEG_RX13+

C94

PEG_RX13-

C95

PEG_TX14+

D98

PEG_TX14-

D99

PEG_RX14+

C98

PEG_RX14-

C99

PEG_TX15+

D101

PEG_TX15-

D102

PEG_RX15+

C101

PEG_RX15-

C102

PEG_LANE_RV#

D54

I CMOS

3.3V / 3.3V

None

PCI Express Graphics lane reversal input strap. Pull low on the Carrier

board to reverse lane order.

PEG_ENABLE#

D97

I CMOS

3.3V /3.3V

None

Strap to enable PCI Express x16 external graphics interface. Pull low to

enable the x16 PEG interface.

Signal

Pin#

Pin Type

Pwr Rail /Tolerance

PU/PD

Description

EXCD0_CPPE#

A49

EXCD1_CPPE#

B48

EXCD0_PERST#

A48

EXCD1_PERST#

B47

O PCIE

AC coupled on Module None

PCI Express Graphics transmit differential pairs 13

I PCIE

AC coupled off Module None

PCI Express Graphics receive differential pairs 13

O PCIE

AC coupled on Module None

PCI Express Graphics transmit differential pairs 15

I PCIE

AC coupled off Module None

PCI Express Graphics receive differential pairs 15

O PCIE

AC coupled on Module None

PCI Express Graphics transmit differential pairs 14

I PCIE

AC coupled off Module None

PCI Express Graphics receive differential pairs 14

ExpressCard Signals Descriptions

I CMOS

3.3V /3.3V

PU 10K to 3.3V

PCI ExpressCard: PCI Express capable card request, active low, one per card

O CMOS

3.3V /3.3V

PU 2.2K to 3.3V

PCI ExpressCard: reset, active low, one per card