Schematics, Z8 encore! xp, F0822 series development kit user manual – Zilog Z8F0411 User Manual

Page 14: F0822 series evaluation board, Connector 2 connector 1 for reference only, Reset

10

UM015009-0608

Schematics

Z8 Encore! XP

®

F0822 Series Development Kit

User Manual

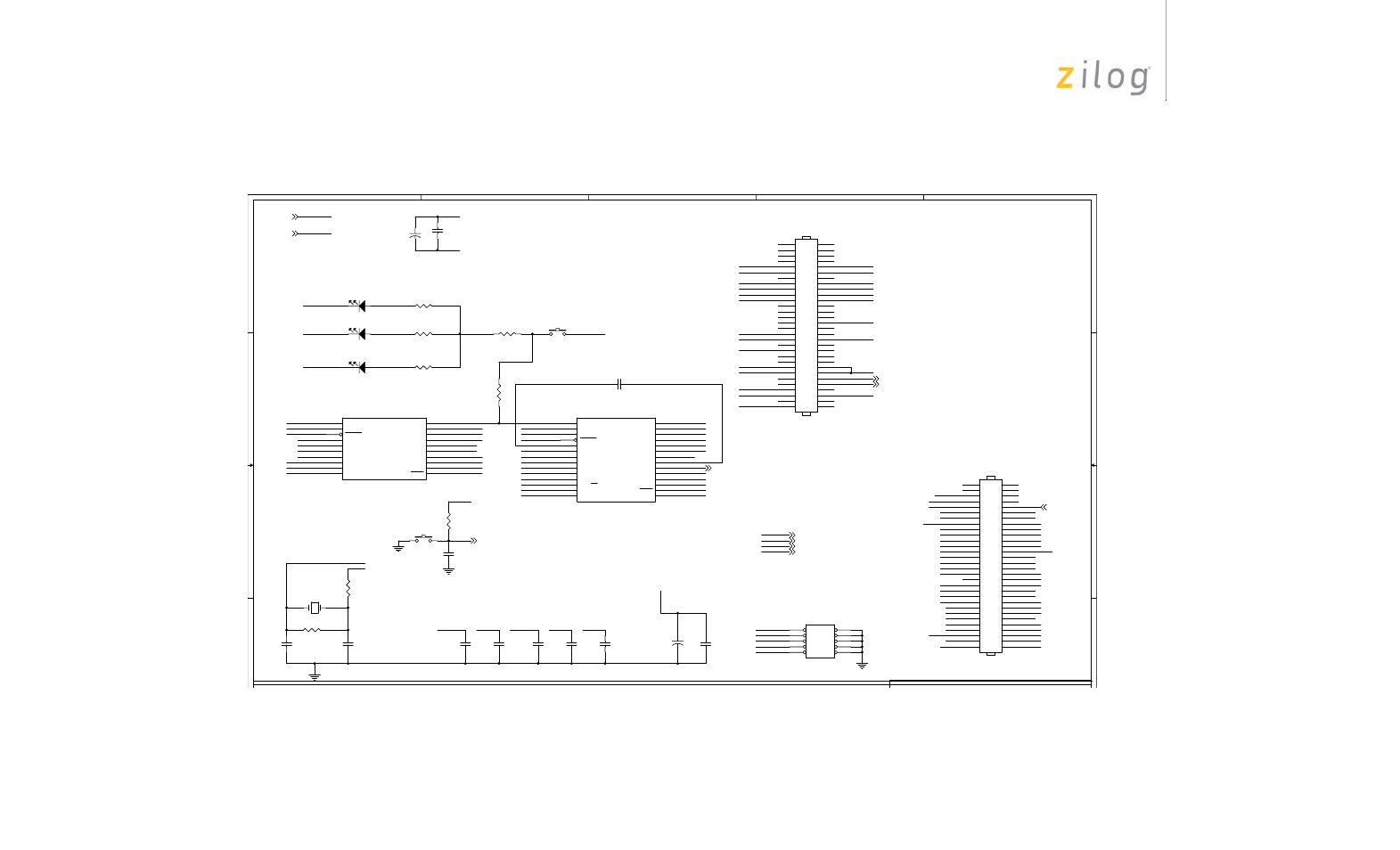

Schematics

and

displays the schematics for Z8 Encore! XP

®

F0822 Series Evaluation Board.

Figure 3. Schematic for Z8 Encore! XP F0822 Series Evaluation Board

5

4

3

2

1

D

D

C

C

B

B

A

A

connector 2

connector 1

for

reference

only

20 pin Socket

28 pin Socket

RESET

If Module is plugged onto the Dev Platform the local

RS232 interface is disabled by pin 50 of JP2

TEST

PB0_ANA0

PB2_ANA2

VCC_33V

PB4_ANA4

PA4_RXD0

PA5_TXD0

PB1_ANA1

PA3_CTS0

VR

EF

AGND

GND

PB3_ANA3

GND

XIN

PB1_ANA1

PB3_ANA3

PB0_ANA0

PB4_ANA4

PB2_ANA2

PB1_ANA1

PB3_ANA3

PB0_ANA0

PB4_ANA4

PB2_ANA2

PB1_ANA1

PB0_ANA0

PA6_SCL

PA6_SCL

PA0_T0IN

PA0_T0IN

-RESET

-RESET

PC2_SS

PA1_T0OUT

PA1_T0OUT

PA2

PA2

PA3_CTS0

PA4_RXD0

PA5_TXD0

DBG

VCC_33V

AGND

PC0_T1IN

PA7_SDA

GND

XIN

XOUT

VCC_33V

PC3_SCK

PC4_MOSI

PC5_MISO

VCC_33V

XOUT

XIN

AGND

DBG

PC1_T1OUT

PA5_TXD0

PA4_RXD0

PA3_CTS0

DBG

PA7_SDA

XOUT

VREF

VREF

A20

-CS0

A12

-IOREQ

-F91_WE

A13

GND

GND

A17

A21

VCC_33V

A14

D1

VCC_33V

D7

-DIS_FLASH

GND

A6

A0

D3

D6

-BUSACK

A3

D2

VCC_33V

A15

A4

-TRSTN

D0

-MREQ

A7

A10

A9

A16

A18

A11

-INSTRD

A19

A5

GND

D5

-CS1

A22

A1

A2

-CS2

-RD

A8

GND

D4

A23

-WR

-BUSREQ

GND

PA7_SDA

PA3_CTS0

PC2_SS

VCC_33V

PC4_MOSI

VCC_33V

PC1_T1OUT

PC0_T1IN

PA2

PA1_T0OUT

GND

GND

PC5_MISO

PA4_RXD0

PA5_TXD0

-RESET

VCC_33V

GND

GND

PA6_SCL

PA0_T0IN

PC3_SCK

PA0_T0IN

PA1_T0OUT

PA2

VCC_33V

GND

VCC_33V

GND

PC0_T1IN

-DIS_IrDA

VCC_33V

-RESET

GND

VCC_33V

GND

PA5_TXD0

PA4_RXD0

PA3_CTS0

VCC_33V

DBG

DBG

VCC_33V

-DIS_IRDA

-DIS_232

-RESET

C16

18pF

D2

RED

2

1

C21

0.001uF

SW2

J2

Header 5x2

1

2

3

4

5

6

7

8

9

10

R12

100

R9

100

U8

Z8F0XX2

1

2

3

4

6

7

9

10

11

12

13

14

15

16

17

18

19

20

24

25

26

27

28

5

8

21

22

23

PC0/T1IN

PA6/SCL

PA7/SDA

RESET

XIN

XOUT

PC5/MISO

PC4/MOSI

PC3/SCK

PC2/SS

PA0/T0IN

PA1/T0OUT

PA2/DE

PA3/CTS0

PA4/RXD0

PA5/TXD0

PC1/T1OUT

DBG

PB4/ANA4

PB3/ANA3

PB2/ANA2

PB1/ANA1

PB0/ANA0

VSS

VDD

AVDD

AVSS

VREF

Y1

18.432MHz

SW1

R10

100K

R14

100K

D3

GREEN

2

1

R11

100

C4

0.1uF

C18

0.001uF

C17

0.001uF

C13

0.01uF

+

C12

22uF

C19

0.001uF

C22

0.01uF

D4

YELL

2

1

C10

0.01uF

+

C14

22uF

JP2

HEADER 30x2/SM

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

R13

220

C15

18pF

R3

10K

C20

0.001uF

JP1

HEADER 30x2/SM

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

R8

100

U7

Z8F0xx1

11

10

9

8

3

6

5

19

18

17

20

14

2

1

13

12

7

4

15

16

PA3/CTS0

PA2/DE

PA1/T0OUT

PA0/T0IN

RESET

XOUT

XIN

PB0/ANA0

PB1/ANA1

VREF

PC0/T1IN

DBG

PA7/SDA

PA6/SCL

PA5/TXD0

PA4/RXD0

VDD

GND

AVDD

AGND