Signal flow and processing, D series tesira quick start guide rev 1.2.0 – Lab.gruppen D Series 80:4T/Ta User Manual

Page 15

12. Signal flow and processing

D SERIES Tesira Quick Start Guide rev 1.2.0

15

12. Signal flow and processing

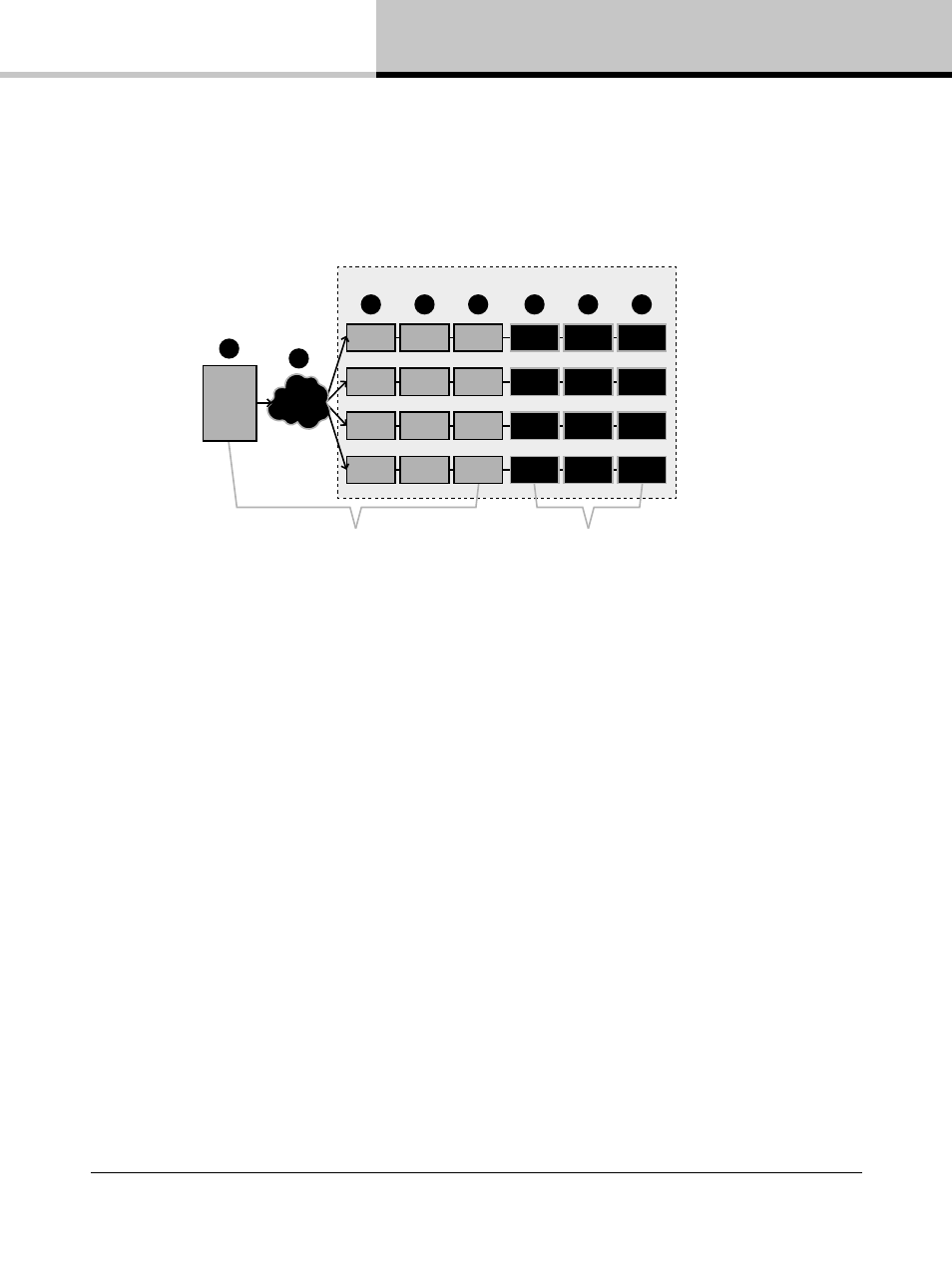

The table below depicts the audio signal flow for a D Series Tesira device.

1 The Tesira system is a free wire DSP environment where processing features can be designed and distributed

among servers. System IO is designed and managed, and all signal processing is defined, at the server level.

D Series Tesira amplifiers are added as high power outputs to the system with audio transported to them via

the AVB network, through analog connection, or both.

2 AVB is a distributed network of one or more Ethernet AVB-enabled switches that carry both networked audio

and control.

3 Mute block in the Tesira output section

4 Level block in the Tesira output section

5 Invert block in the Tesira output section

6 Amplifier gain - Digitally implemented for exact control and management of gain structure

7 ISVPL/RPM - Inter-sample Voltage Peak Limiter is a digitally implemented voltage peak limiter with assignable

profiles. Rational Power Management configuration enables flexible power sharing of the total available power

across the amplifier channels.

8 Load monitoring - Impedance sweeps and LoadPilot monitoring

Mute

Level

Invert

AmpGain

RPM/ISVPL

Load

Monitoring

Mute

Level

Invert

AmpGain

RPM/ISVPL

Load

Monitoring

Mute

Level

Invert

AmpGain

RPM/ISVPL

Load

Monitoring

Level

AmpGain

RPM/ISVPL

Load

Monitoring

D Series Tesira Amplifier

1

2

3

4

5

6

7

8

AVB

Network

Mute

Invert

Tesira

Environment

Amplifier

Platform

Tesira

freewire DSP

processing

hosted by

Tesira

servers