Hatteland Display 13 inch - HD 13T21 MMC (Widescreen, Inte Ato CPU) User Manual

Page 5

DOC101200-2_AIPC_API_Registers_SMBus_Linux[1].docx - rev 03 – 2013-12-03 - Created by:6923

Page 5 of 6

Hatteland Display AS, Åmsosen, N-5578 Nedre Vats, Norway

Tel: (+47) 4814 2200 - [email protected] - www.hatteland-display.com

All intellectual properties belong to Hatteland Display AS

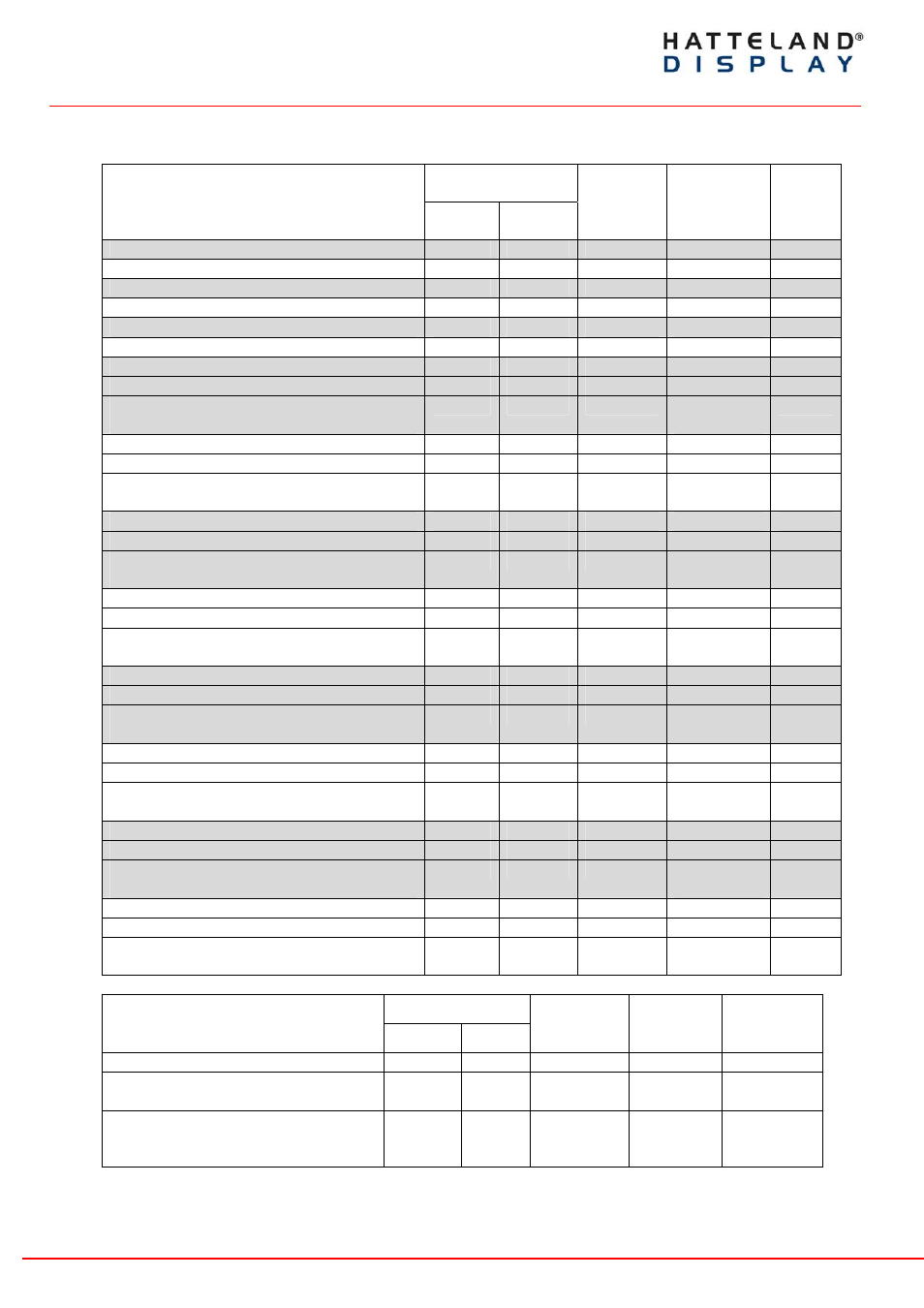

Device Address

Command

Base R/#W

Register

Address

Input Data Numb

er of

output

bytes

ALARM_RESET

0x48

0

0x24

0x00

-

ALARM_FAULT_TEST

0x48 0 0x25

0x00 -

ALARM_SOUND_OFF

0x48

0

0x26

0x00

-

ALARM_ACK

0x48 0 0x27

0x00 -

IO_STATUS_RETURN

0x48

1

0x28

-

1

IO_STATUS_RETURN

0x48

0

0x28

0xXX -

ERROR_LED_EN

1) Read IO_STATUS_RETURN

0x48

1

0x28

-

1

2) Bit 0 shall be set to 1. Rest of the

bits same value as output from 1).

0x48

0

0x28

0xXX

(Bit 0=1)

-

ERROR_LED_DIS

1) Read IO_STATUS_RETURN

0x48 1 0x28

-

1

2) Bit 0 shall be set to 0. Rest of the

bits same value as output from 1).

0x48 0 0x28 0xXX

(Bit 0=0)

-

K1_EN

1) Read IO_STATUS_RETURN

0x48

1

0x28

-

1

2) Bit 1 shall be set to 1. Rest of the

bits same value as output from 1).

0x48

0

0x28

0xXX

(Bit 1=1)

-

K1_DIS

1) Read IO_STATUS_RETURN

0x48 1 0x28

-

1

2) Bit 1 shall be set to 0. Rest of the

bits same value as output from 1).

0x48 0 0x28 0xXX

(Bit 1=0)

-

HS_EN

1) Read IO_STATUS_RETURN

0x48

1

0x28

-

1

2) Bit 2 shall be set to 1. Rest of the

bits same value as output from 1).

0x48

0

0x28

0xXX

(Bit 2=1)

-

HS_DIS

1) Read IO_STATUS_RETURN

0x48 1 0x28

-

1

2) Bit 2 shall be set to 0. Rest of the

bits same value as output from 1).

0x48 0 0x28 0xXX

(Bit 2=0)

-

BUZZER_EN

1) Read IO_STATUS_RETURN

0x48

1

0x28

-

1

2) Bit 3 shall be set to 1. Rest of the

bits same value as output from 1).

0x48

0

0x28

0xXX

(Bit 3=1)

-

BUZZER_DIS

1) Read IO_STATUS_RETURN

0x48 1 0x28

-

1

2) Bit 3 shall be set to 0. Rest of the

bits same value as output from 1).

0x48 0 0x28 0xXX

(Bit 3=0)

-

Device Address

Command

Base R/#W

Register

Address

Input

Data

Number of

output

bytes

BACK_LIGHT_ADJUSTMENT 0x48

1

0x11 - 1

BACK_LIGHT_ADJUSTMENT

0x48

0

0x11

0xXX

[0-255]

BACK_LIGHT_PWM

0x48 0 0x15

0xXXXX

[0-

60000]