North bridge, 1 cas # latency (tcl), 2 ras # active time (tras) – Avalue ESM-QM57 User Manual

Page 67: 3 row precharge time (trp)

User

’s Manual

ESM- QM57 User

’s Manual

67

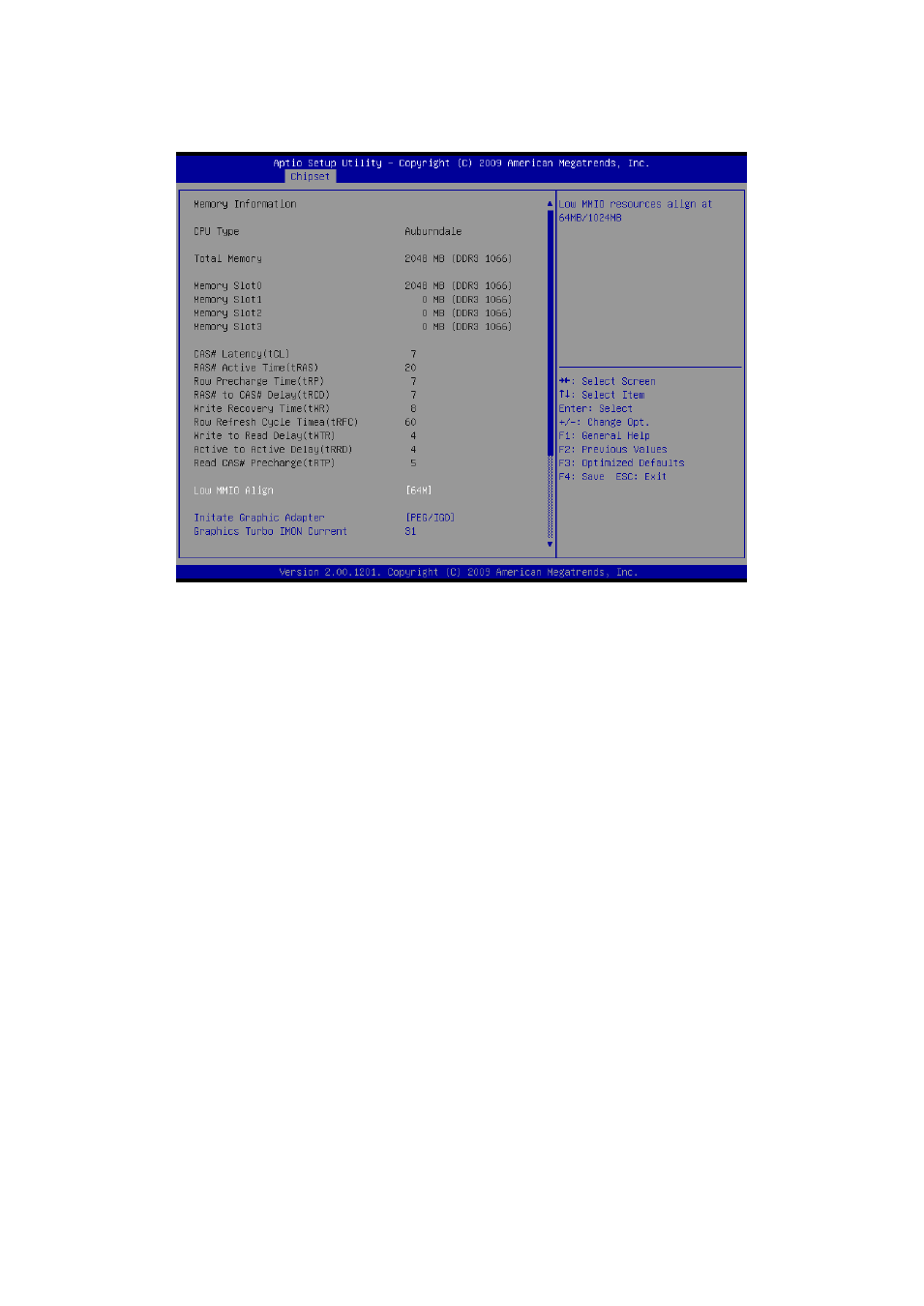

3.6.3.1

North Bridge

3.6.3.1.1 CAS # Latency (tCL)

This item controls the time delay (in clock cycles - CLKs) that passes before the SDRAM

starts to carry out a read command after receiving it. This also determines the number of

CLKs for the completion of the first part of a burst transfer. In other words, the lower the

latency, the faster the transaction.

3.6.3.1.2 RAS # Active Time (tRAS)

It allows controlling the memory bank's minimum row active time (tRAS). This constitutes

the time when a row is activated until the time the same row can be deactivated. If the tRAS

period is too long, it can reduce performance by unnecessarily delaying the deactivation of

active rows. Reducing the tRAS period allows the active row to be deactivated earlier.

If the tRAS period is too short, there may not be enough time to complete a burst transfer.

This reduces performance and data may be lost or corrupted.

3.6.3.1.3 Row Precharge Time (tRP)

This option sets the number of cycles required for the RAS to accumulate its charge before

the SDRAM refreshes.

.