5 adc timing control, 1 timebase, 2 dds timing vs. adc – ADLINK PCIe-9529 User Manual

Page 37: 3 filter delay in adc, Adc timing control, Timebase, Dds timing vs. adc, Filter delay in adc, Figure 3-9, Timebase architecture

Operations

27

PCIe-9529

3.5 ADC Timing Control

3.5.1

Timebase

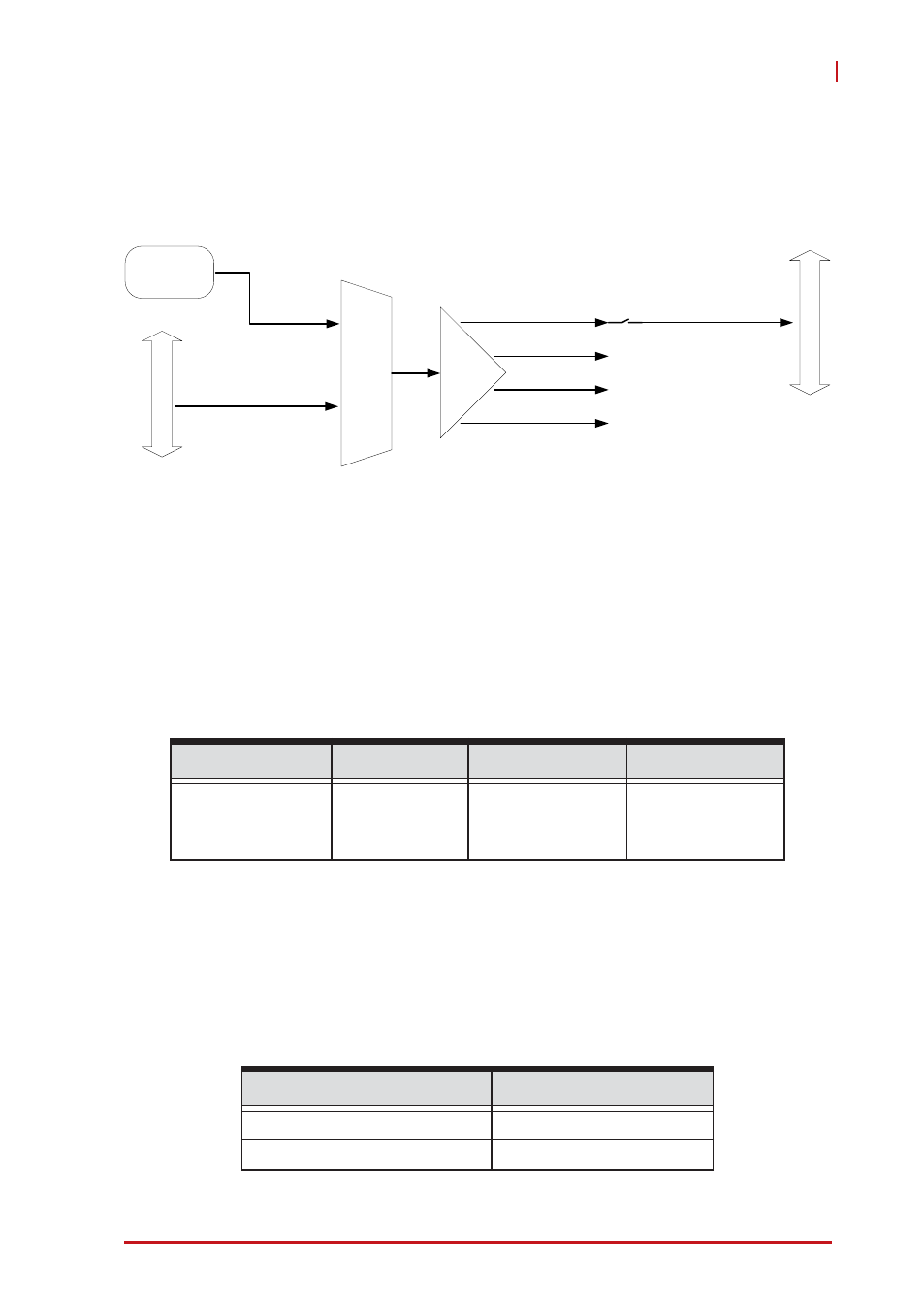

Figure 3-9: Timebase Architecture

An onboard timebase clock drives the sigma-delta ADC, with fre-

quency exceeding the sample rate and produced by a PLL chip,

with output frequency programmable to superior resolution. The

PCIe- 9529 accepts the external timebase from SSI Bus Number 0

for synchronization between modules.

3.5.2

DDS Timing vs. ADC

Table 3-5: Timing Relationship between ADC and PLL Clock

3.5.3

Filter Delay in ADC

Filter delay indicates time required for data propagation through a

converter. Both AI channels experience filter delay due to filter

circuitry and converter architecture, as shown.

Sampling Rate

8k – 54kS/s

54k - 108kS/s

108 k – 192kS/s

DDS(PLL) CLK

6.144

M-41.472

MHz

13.824

M-27.648 MHz

20.736

M-36.864 MHz

Update Rate (kS/s)

Filter Delay (samples)

8 K - 54 kS/s

13

54 K - 108 kS/s

13

Timebase Clock Mux

SSI Bus [0]

SSI_TIMEBASE

SSI Bus

[0]

SSI_TIMEBASE

Onboard

Oscillator

10M

ADC0_CLK

ADC1_CLK

FPGA_MCLK

1-to-4 Clock

Buffer & PLL

SYNC_CLK