2 ssi timebase, 3 ssi_trig, 4 ssi__pre_data_rdy – ADLINK PCIe-9852 User Manual

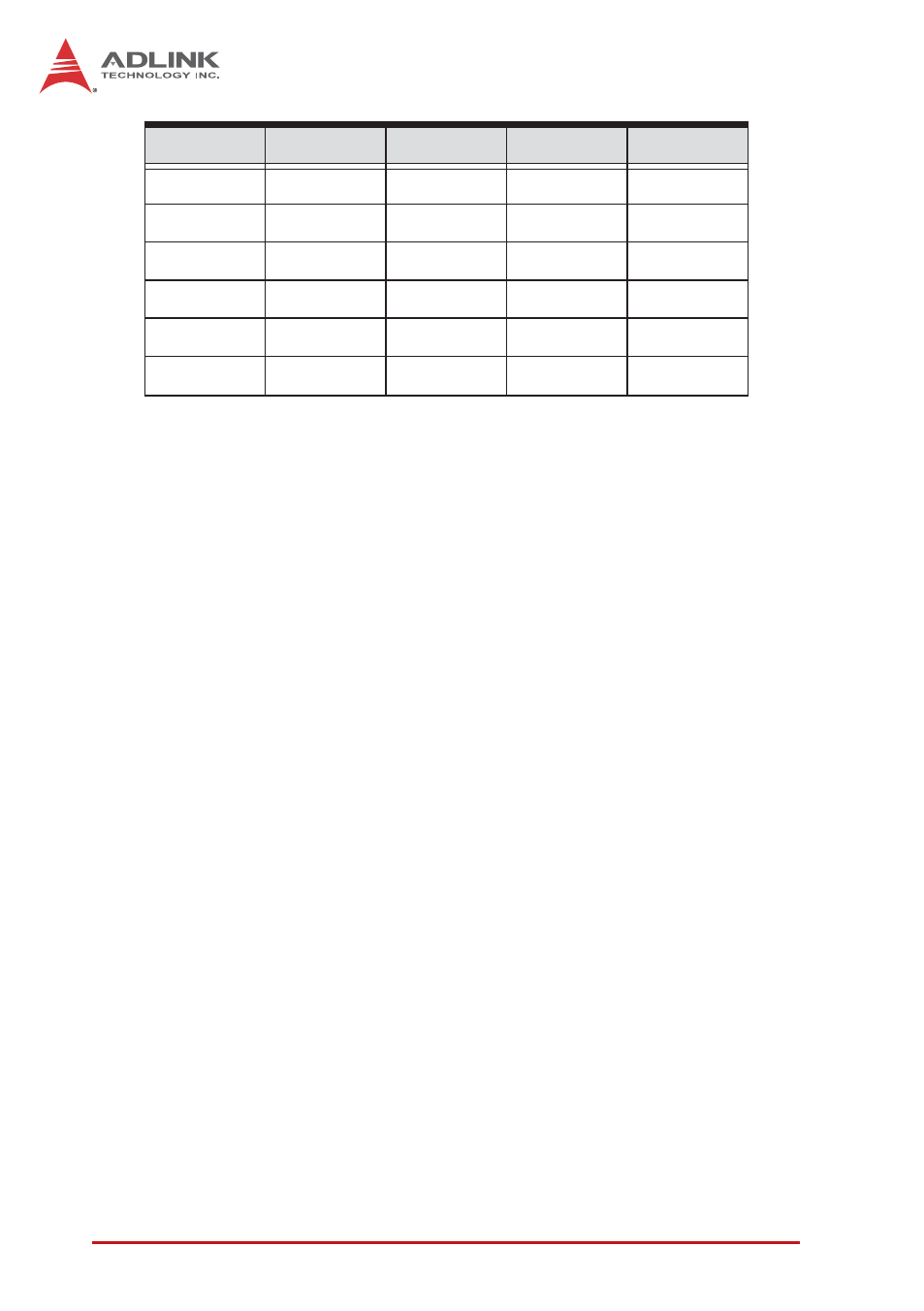

Page 38: Ssi timebase, Ssi_trig, Ssi__pre_data_rdy, Table 3-6: card number configuration settings

28

Operations

Table 3-6: Card Number Configuration Settings

Default card number is 0.

3.7.2

SSI Timebase

As an output, the SSI_TIMEBASE signal outputs the onboard

10MHz through ACL-eSSI-2/ACLeSSI-3/ACL-eSSI-4 cables. As

an input, the PCIe-9852 accepts the SSI_TIMEBASE signal to be

the source of timebase.

3.7.3

SSI_TRIG

As an output, the SSI_TRIG signal reflects the trigger event signal

in an acquisition sequence. As an input, the PCIe-9852 accepts

the SSI_TRIG signal to be the trigger event source. The signal is

configured in the rising edge-detection mode.

3.7.4

SSI__pre_data_rdy

If one SSI slave is set to mid-trig or pre-trig mode, the SSI master

should also be in mid-trig or pre-trig mode. SSI slaves in mid-trig

or pre-trig mode should send pre_data_rdy to SSI master through

SSI[0], SSI[1], SSI[5] or SSI[6].

A SSI master sends SSI_trig to other SSI slaves. If set to pre-trig

or mid-trig mode, SI_pre_data_rdy is received from other SSI

slaves. SSI slaves should be set to mid-trig or pre-trig mode to

send SSI_pre_data_rdy signal to the SSI master. Different SSI

slaves should not use the same SSI pins.

OFF

ON

OFF

ON

10

OFF

ON

OFF

OFF

11

OFF

OFF

ON

ON

12

OFF

OFF

ON

OFF

13

OFF

OFF

OFF

ON

14

OFF

OFF

OFF

OFF

15

Slider 1

Slider 2

Slider 3

Slider 4

Card #