5 timebase, 1 internal reference clock, Data average mode – ADLINK PCIe-9852 User Manual

Page 31: Timebase, Internal reference clock, Figure 3-9, Re-trigger mode acquisition, Figure 3-10, Pcie-9852 clock architecture

Operations

21

PXIe-9852

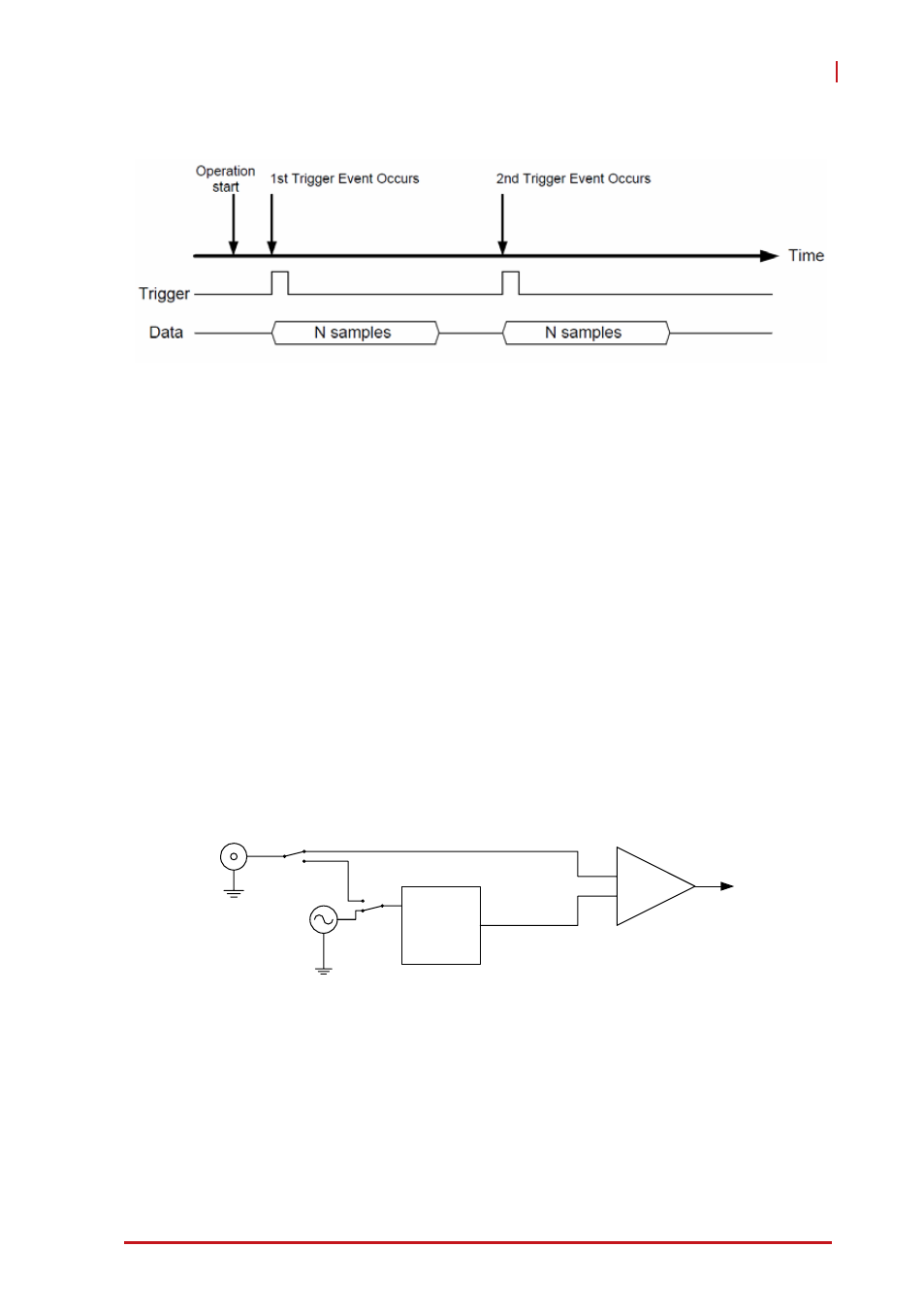

Figure 3-9: Re-Trigger Mode Acquisition

3.4.6

Data Average Mode (Post-Trigger and Delayed-

Trigger only)

In normal post-trigger mode acquisition, N samples/channel data

are generated for a single trigger event. In Re-trigger mode (See

“Acquisition with Re-Triggering” on page 20.), a total of N * R sam-

ples/channel data is generated for R trigger events, that is, R

traces (A trace contains N samples/channel). In Data Average

Mode, only N samples/channel data are generated for R trigger

events. The single trace data (N samples/channel) is the average

of the R traces sample by sample.

3.5 Timebase

Figure 3-10: PCIe-9852 Clock Architecture

3.5.1

Internal Reference Clock

The PCIe-9852 internal 10MHz Crystal oscillator acts as reference

clock, generating, after synthesis, precisely 200MHz clock for

ADC.

Synthesizer

Clock buffer

To ADC

CLK IN

10MHz

Xtal